# **MELSEC System Q**

**Programmable Logic Controllers**

**User's Manual**

## **HART Analog Input Module**

### **ME1AD8HAI-Q**

# About this Manual

The texts, illustration, diagrams and examples in this manual are provided for information purposes only. They are intended as aids to help explain the installation, operation, programming and use of the programmable logic controllers of the MELSEC System Q.

If you have any questions about the installation and operation of any of the products described in this manual please contact your local sales office or distributor (see back cover).

You can find the latest information and answers to frequently asked questions on our website at [www.mitsubishi-automation.com](http://www.mitsubishi-automation.com).

MITSUBISHI ELECTRIC EUROPE BV reserves the right to make changes to this manual or the technical specifications of its products at any time without notice.

© 2009 –2013

| <b>HART Analog Input Module</b><br><b>ME1AD8HAI-Q</b><br><b>User's Manual</b><br><b>Art.-no.: 229753</b> |         |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------|---------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Version</b>                                                                                           |         | <b>Changes / Additions / Corrections</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A                                                                                                        | 10/2009 | pdp-dk                                   | First edition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| B                                                                                                        | 03/2010 | pdp-dk                                   | <ul style="list-style-type: none"><li>• New section 3.5.25: HART device information refresh interval (Un\G191)</li><li>• Addition of Un\G191 to buffer memory assignment in section 3.5.1</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C                                                                                                        | 12/2010 | pdp-dk                                   | <ul style="list-style-type: none"><li>• Correction in section 3.2 (Specifications, accuracy): "digital output value" was changed to "digital output range"; "Photo coupler isolation" was changed to "Digital isolator insulation"</li><li>• Correction in section 3.2.2 (Accuracy)</li><li>• Correction in section 4.1: Subitem "A protective film is attached to the..." was removed – Modul has no protective film.</li><li>• Correction in section 6.4: "..., the LED ON status..." in the first sentence was removed.</li><li>• Correction on page 1-2 and corresponding on page 3-6: "...is output..." was changed to ...is triggered..." in 3 sentences.</li></ul> |

| D                                                                                                        | 02/2012 | pdp-dk                                   | <ul style="list-style-type: none"><li>• Correction on page 3-47: Meaning of the bits in buffer memory address 53 in Fig. 3-29</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| E                                                                                                        | 01/2013 | pdp-dk                                   | <ul style="list-style-type: none"><li>• New chapter 5: "Intelligent Function Utility (GX Works2)"</li><li>• Addition of the "Intelligent function utility" in section 1.1</li><li>• Update of table 2-1 and the item "Supported software packages" in section 2.1</li><li>• Changes in section 2.2</li><li>• Note in table 3-8 (entry for X9)</li><li>• Note regarding initial settings in Fig. 6-1</li></ul>                                                                                                                                                                                                                                                             |

|                                                                                                          |         |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# Safety Guidelines

## For use by qualified staff only

This manual is only intended for use by properly trained and qualified electrical technicians who are fully acquainted with the relevant automation technology safety standards. All work with the hardware described, including system design, installation, configuration, maintenance, service and testing of the equipment, may only be performed by trained electrical technicians with approved qualifications who are fully acquainted with all the applicable automation technology safety standards and regulations. Any operations or modifications to the hardware and/or software of our products not specifically described in this manual may only be performed by authorised Mitsubishi Electric staff.

## Proper use of the products

The programmable logic controllers of the MELSEC System Q are only intended for the specific applications explicitly described in this manual. All parameters and settings specified in this manual must be observed. The products described have all been designed, manufactured, tested and documented in strict compliance with the relevant safety standards. Unqualified modification of the hardware or software or failure to observe the warnings on the products and in this manual may result in serious personal injury and/or damage to property. Only peripherals and expansion equipment specifically recommended and approved by Mitsubishi Electric may be used with the programmable logic controllers of the MELSEC System Q.

All and any other uses or application of the products shall be deemed to be improper.

## Relevant safety regulations

All safety and accident prevention regulations relevant to your specific application must be observed in the system design, installation, configuration, maintenance, servicing and testing of these products. The regulations listed below are particularly important in this regard. This list does not claim to be complete, however; you are responsible for being familiar with and conforming to the regulations applicable to you in your location.

### ● VDE Standards

- VDE 0100

Regulations for the erection of power installations with rated voltages below 1000 V

- VDE 0105

Operation of power installations

- VDE 0113

Electrical installations with electronic equipment

- VDE 0160

Electronic equipment for use in power installations

- VDE 0550/0551

Regulations for transformers

- VDE 0700

Safety of electrical appliances for household use and similar applications

- VDE 0860

Safety regulations for mains-powered electronic appliances and their accessories for household use and similar applications.

### ● Fire safety regulations

### ● Accident prevention regulations

- VBG Nr.4

Electrical systems and equipment

---

### **Safety warnings in this manual**

In this manual warnings that are relevant for safety are identified as follows:

#### **DANGER:**

*Failure to observe the safety warnings identified with this symbol can result in health and injury hazards for the user.*

#### **WARNING:**

*Failure to observe the safety warnings identified with this symbol can result in damage to the equipment or other property.*

**General safety information and precautions**

The following safety precautions are intended as a general guideline for using PLC systems together with other equipment. These precautions must always be observed in the design, installation and operation of all control systems.

**DANGER:**

- ***Observe all safety and accident prevention regulations applicable to your specific application. Always disconnect all power supplies before performing installation and wiring work or opening any of the assemblies, components and devices.***

- ***Assemblies, components and devices must always be installed in a shockproof housing fitted with a proper cover and fuses or circuit breakers.***

- ***Devices with a permanent connection to the mains power supply must be integrated in the building installations with an all-pole disconnection switch and a suitable fuse.***

- ***Check power cables and lines connected to the equipment regularly for breaks and insulation damage. If cable damage is found immediately disconnect the equipment and the cables from the power supply and replace the defective cabling.***

- ***Before using the equipment for the first time check that the power supply rating matches that of the local mains power.***

- ***Take appropriate steps to ensure that cable damage or core breaks in the signal lines cannot cause undefined states in the equipment.***

- ***You are responsible for taking the necessary precautions to ensure that programs interrupted by brownouts and power failures can be restarted properly and safely. In particular, you must ensure that dangerous conditions cannot occur under any circumstances, even for brief periods.***

- ***EMERGENCY OFF facilities conforming to EN 60204/IEC 204 and VDE 0113 must remain fully operative at all times and in all PLC operating modes. The EMERGENCY OFF facility reset function must be designed so that it cannot ever cause an uncontrolled or undefined restart.***

- ***You must implement both hardware and software safety precautions to prevent the possibility of undefined control system states caused by signal line cable or core breaks.***

- ***When using modules always ensure that all electrical and mechanical specifications and requirements are observed exactly.***

# Contents

## 1 Overview

|     |                |     |

|-----|----------------|-----|

| 1.1 | Features ..... | 1-1 |

|-----|----------------|-----|

## 2 System Configuration

|     |                                                                       |     |

|-----|-----------------------------------------------------------------------|-----|

| 2.1 | Applicable Systems.....                                               | 2-1 |

| 2.2 | How to Check the Function Version and Serial No. of the Modules ..... | 2-3 |

## 3 Detailed Description of the Module

|       |                                                                                                          |      |

|-------|----------------------------------------------------------------------------------------------------------|------|

| 3.1   | Part Names.....                                                                                          | 3-1  |

| 3.1.1 | Signal Layout of the Terminal Block .....                                                                | 3-2  |

| 3.2   | Specifications .....                                                                                     | 3-3  |

| 3.2.1 | I/O conversion characteristic.....                                                                       | 3-4  |

| 3.2.2 | Accuracy .....                                                                                           | 3-4  |

| 3.2.3 | External Dimensions .....                                                                                | 3-5  |

| 3.3   | Functions of the HART Analog Input Module .....                                                          | 3-6  |

| 3.3.1 | A/D conversion methods .....                                                                             | 3-7  |

| 3.3.2 | Maximum and minimum values hold function.....                                                            | 3-9  |

| 3.3.3 | Input signal error detection function .....                                                              | 3-10 |

| 3.3.4 | Warning output function .....                                                                            | 3-11 |

| 3.3.5 | Scaling Function.....                                                                                    | 3-15 |

| 3.3.6 | HART Master Function .....                                                                               | 3-16 |

| 3.4   | I/O Signals for the Programmable Controller CPU.....                                                     | 3-18 |

| 3.4.1 | List of I/O signals .....                                                                                | 3-18 |

| 3.4.2 | Details of I/O signals .....                                                                             | 3-19 |

| 3.5   | Buffer Memory .....                                                                                      | 3-23 |

| 3.5.1 | Buffer memory assignment .....                                                                           | 3-24 |

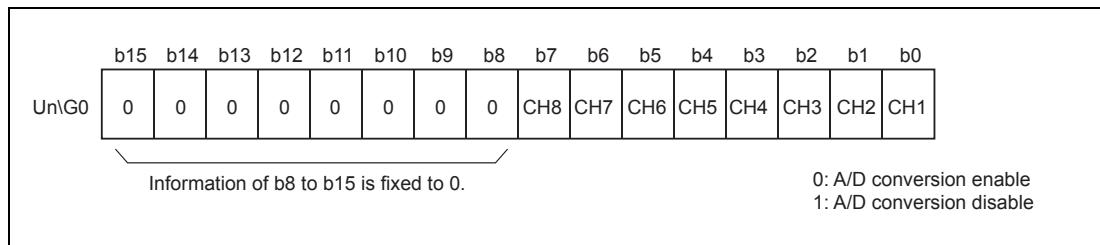

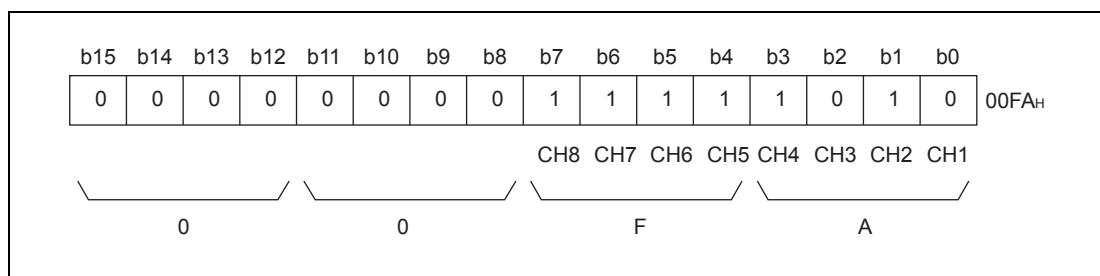

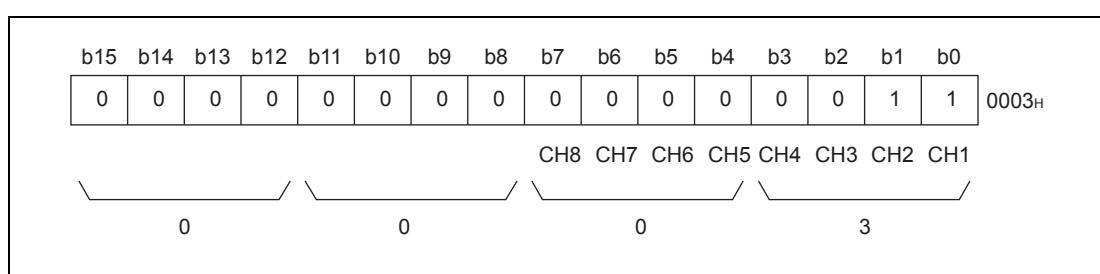

| 3.5.2 | A/D conversion enable/disable setting (Un\G0).....                                                       | 3-40 |

| 3.5.3 | CH1 Average time/Average number of times/Moving average/<br>Time constant settings (Un\G1 to Un\G8)..... | 3-40 |

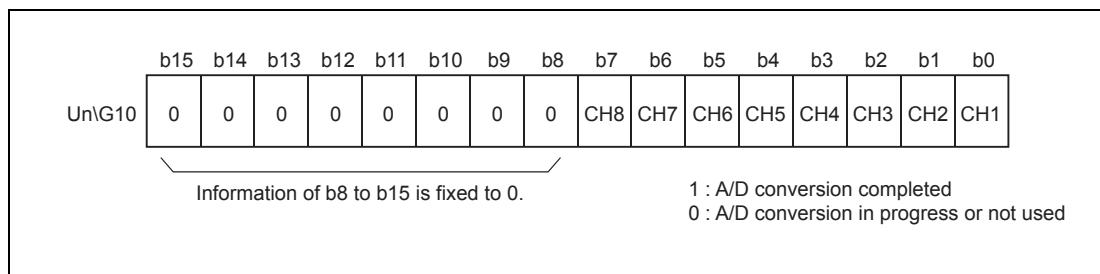

| 3.5.4 | A/D conversion completed flag (Un\G10).....                                                              | 3-41 |

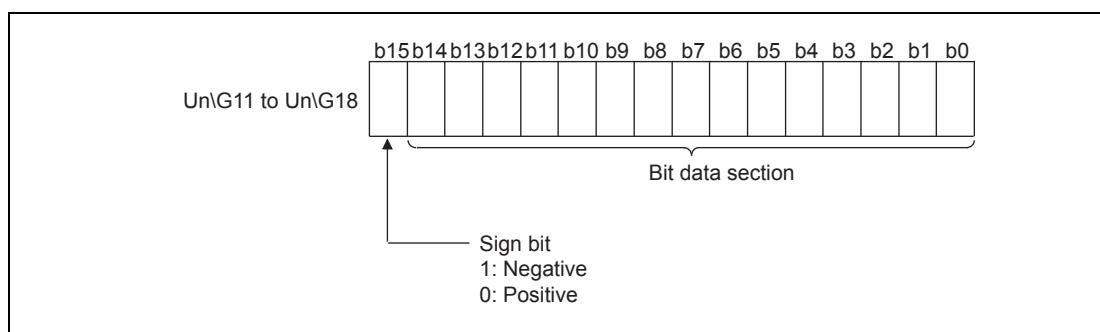

| 3.5.5 | CH1 digital output value (Un\G11 to Un\G18) .....                                                        | 3-41 |

| 3.5.6 | Write data error code (Un\G19).....                                                                      | 3-42 |

|        |                                                                                  |      |

|--------|----------------------------------------------------------------------------------|------|

| 3.5.7  | Setting range (Un\G20, Un\G21).....                                              | 3-42 |

| 3.5.8  | Averaging process specification (Un\G24, Un\G25).....                            | 3-43 |

| 3.5.9  | CHI maximum value/minimum value storage area (Un\G30 to Un\G45).....             | 3-44 |

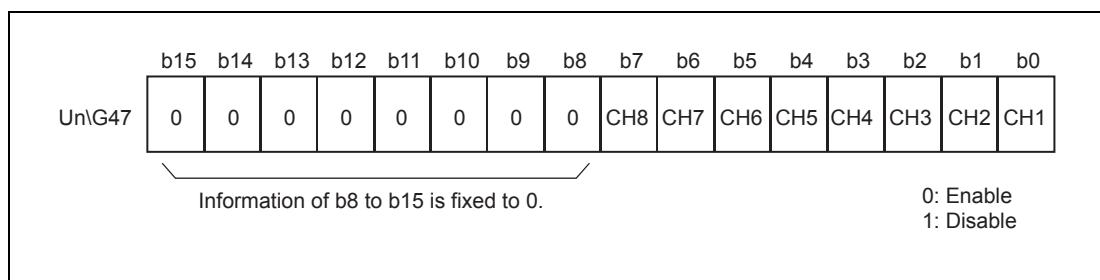

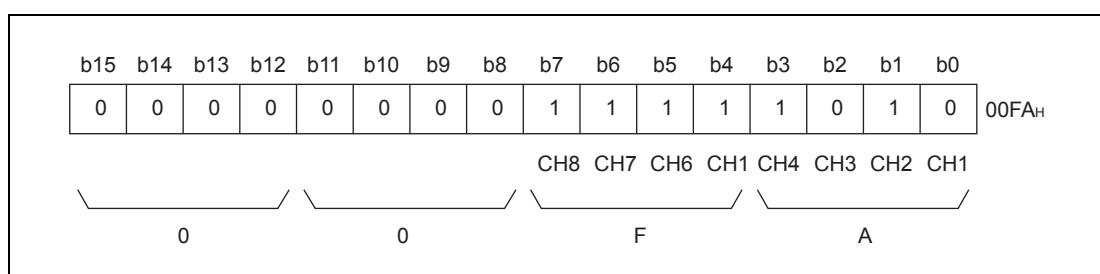

| 3.5.10 | Input signal error detection setting (Un\G47) .....                              | 3-44 |

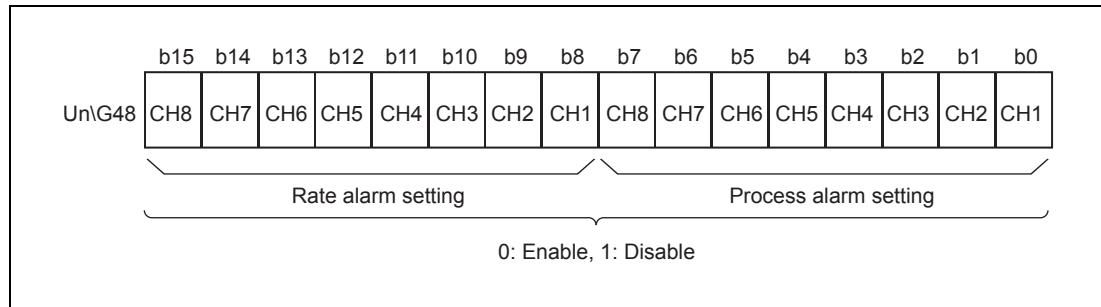

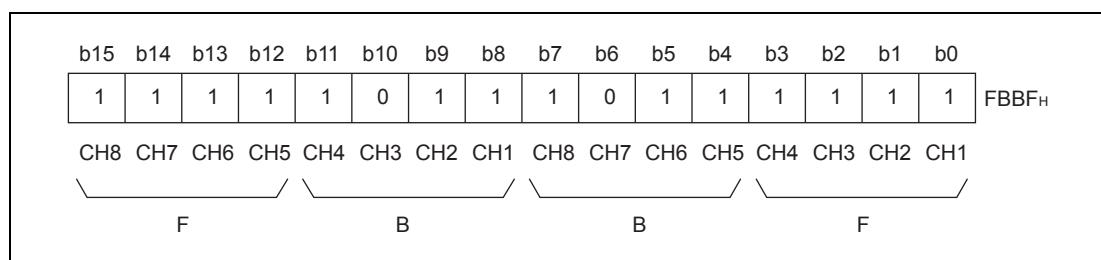

| 3.5.11 | Warning output settings (Un\G48) .....                                           | 3-45 |

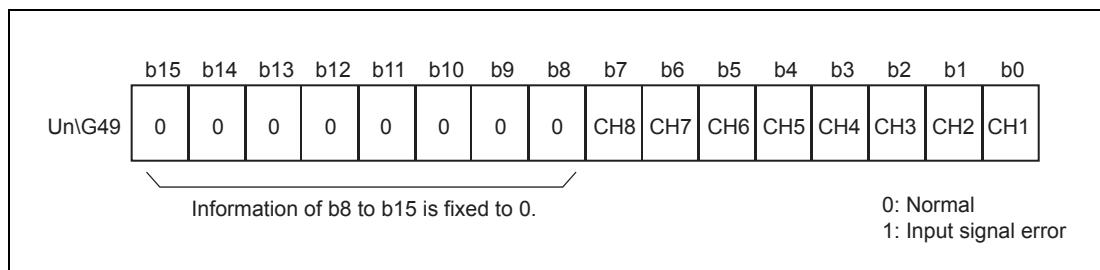

| 3.5.12 | Input signal error detection flag (Un\G49) .....                                 | 3-46 |

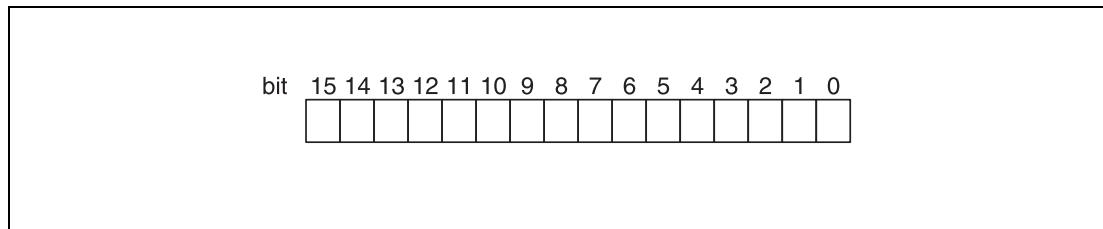

| 3.5.13 | Warning output flag (Un\G50, Un\G51).....                                        | 3-47 |

| 3.5.14 | Scaling enable/disable setting (Un\G53).....                                     | 3-47 |

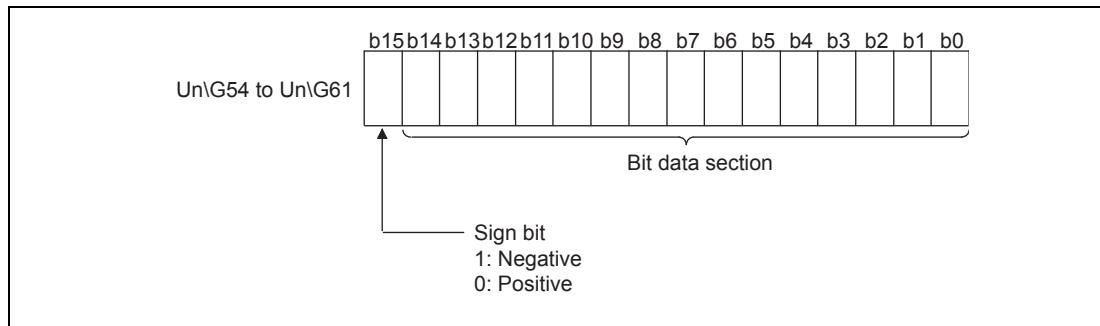

| 3.5.15 | CHI scaling value storage area (Un\G54 to Un\G61) .....                          | 3-48 |

| 3.5.16 | CHI scaling upper/lower limit value (Un\G62 to Un\G77) .....                     | 3-48 |

| 3.5.17 | CHI process alarm upper/lower limit value (Un\G86 to Un\G117) .....              | 3-48 |

| 3.5.18 | CHI rate alarm warning detection period (Un\G118 to Un\G125) .....               | 3-49 |

| 3.5.19 | CHI rate alarm upper/lower limit value (Un\G126 to Un\G141).....                 | 3-50 |

| 3.5.20 | CHI input signal error detection setting value (Un\G142 to Un\G149) .....        | 3-50 |

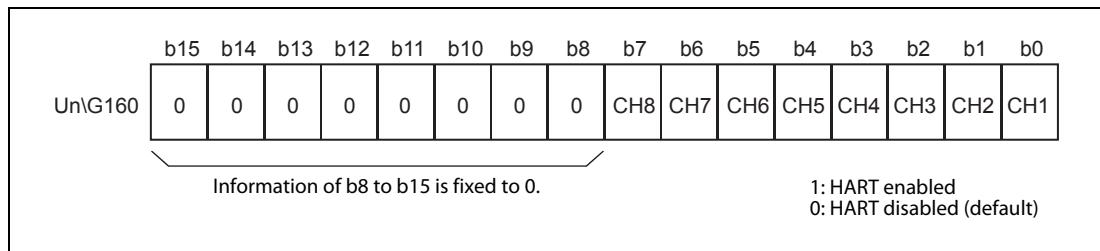

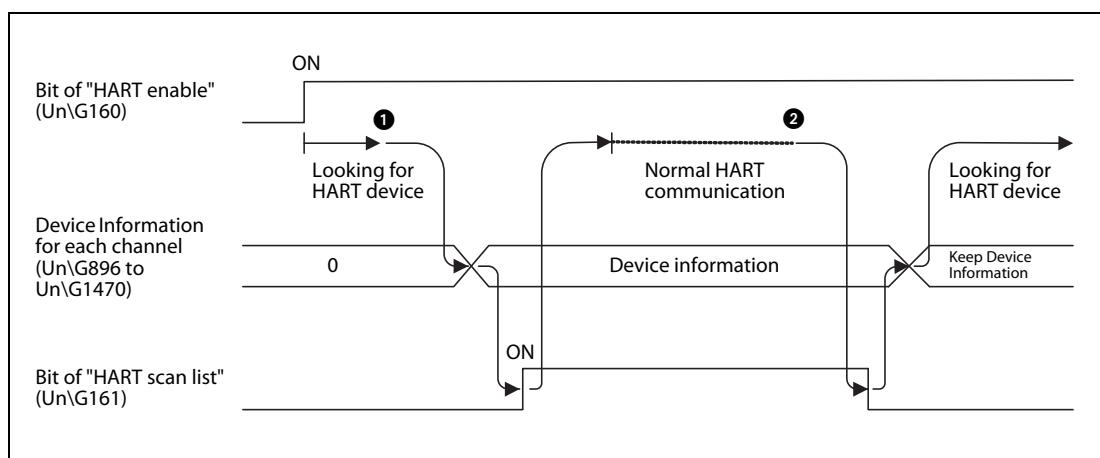

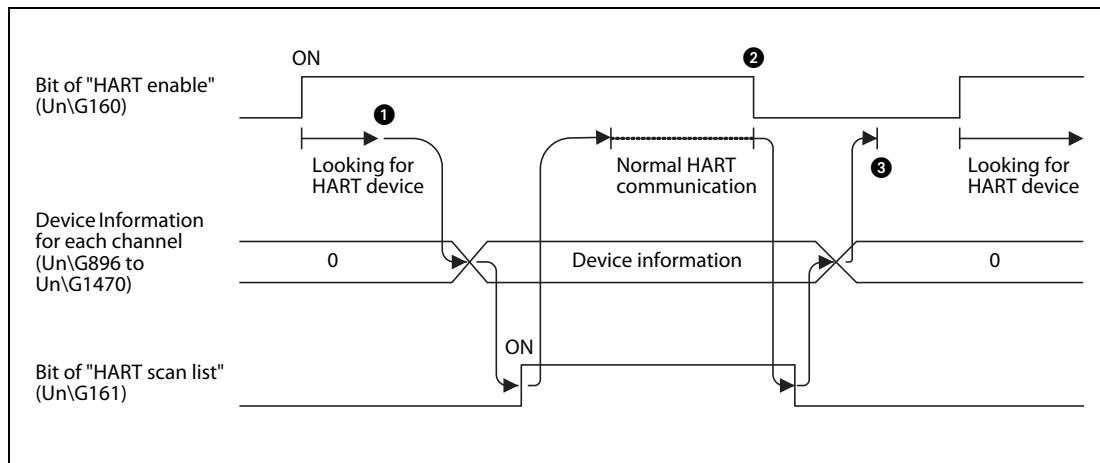

| 3.5.21 | HART enable (Un\G160).....                                                       | 3-51 |

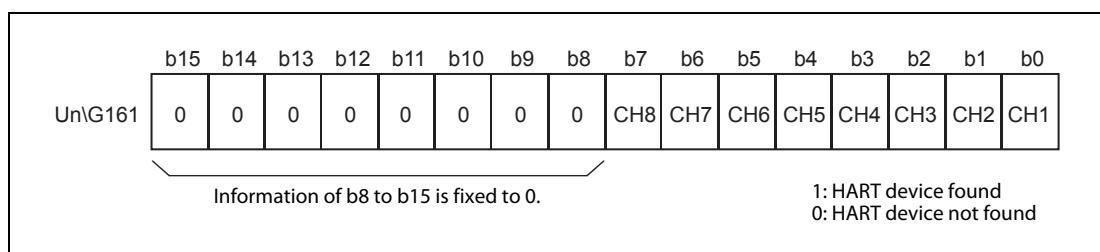

| 3.5.22 | HART scan list (Un\G161).....                                                    | 3-51 |

| 3.5.23 | HART Cycle Time (Un\G162 to Un\G164).....                                        | 3-52 |

| 3.5.24 | HART Maximum Retries (Un\G176 to Un\G183) .....                                  | 3-52 |

| 3.5.25 | HART device information refresh interval (Un\G191) .....                         | 3-52 |

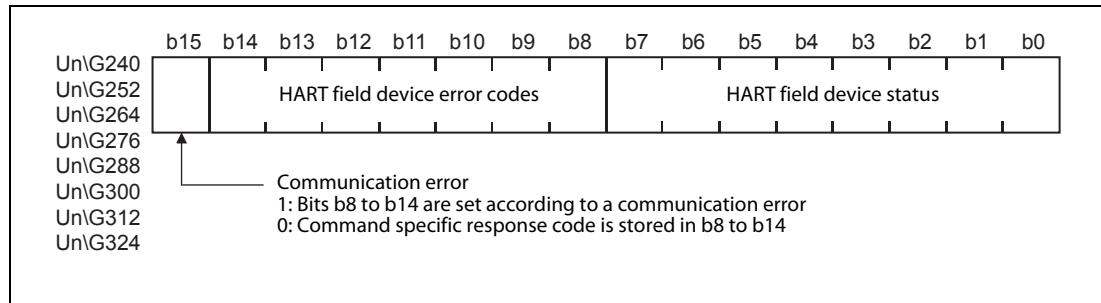

| 3.5.26 | HART Field Device Status (Un\G240, Un\G252, Un\G264...) .....                    | 3-53 |

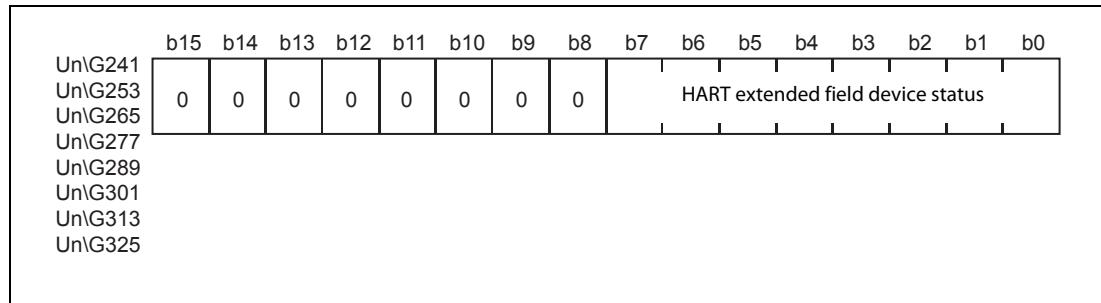

| 3.5.27 | Extended HART Field Device Status (Un\G241, Un\G253, Un\G265...) .....           | 3-54 |

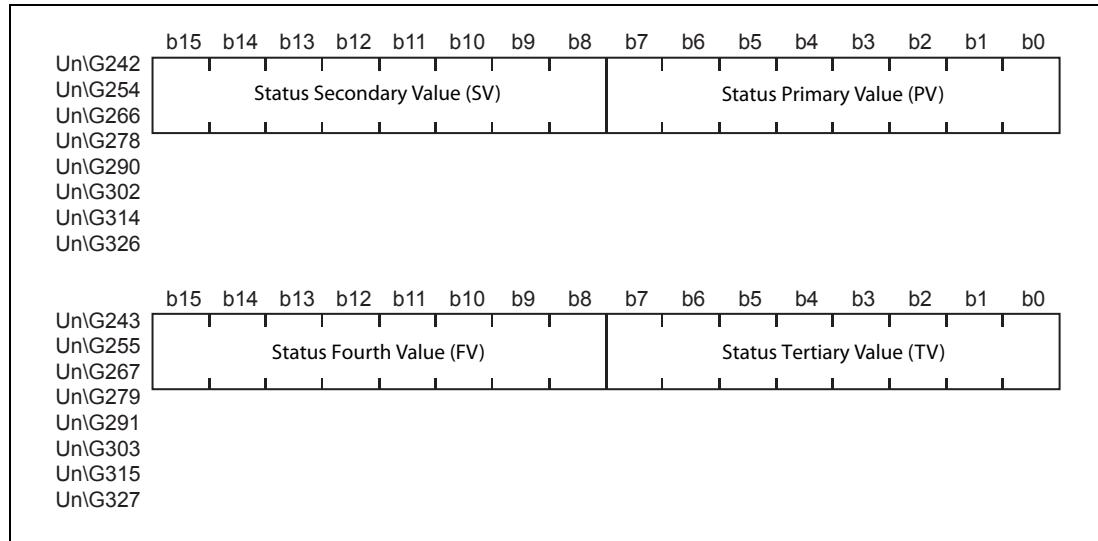

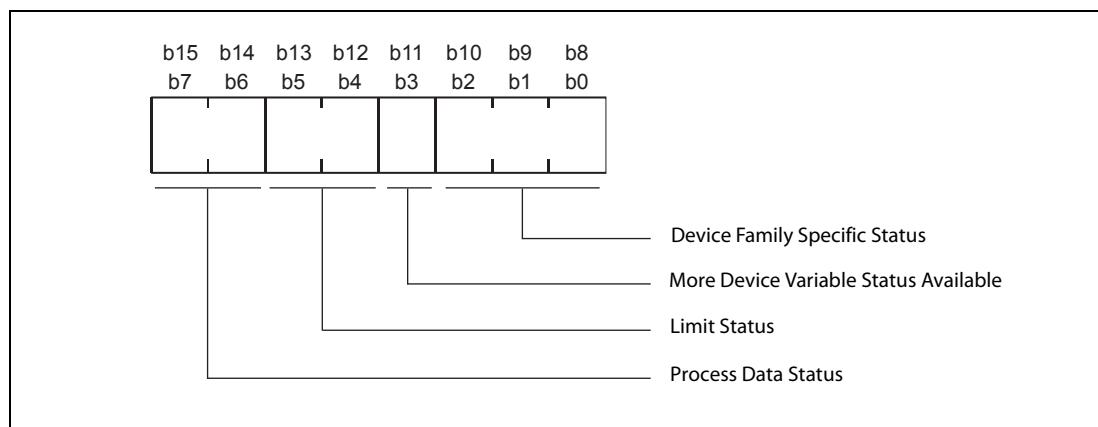

| 3.5.28 | Device Variable Status (Un\G242 & Un\G243, Un\G254 & Un\G255...) .....           | 3-55 |

| 3.5.29 | HART Process Variables (Un\G244 to Un\G251, Un\G256 to Un\G263...) .....         | 3-56 |

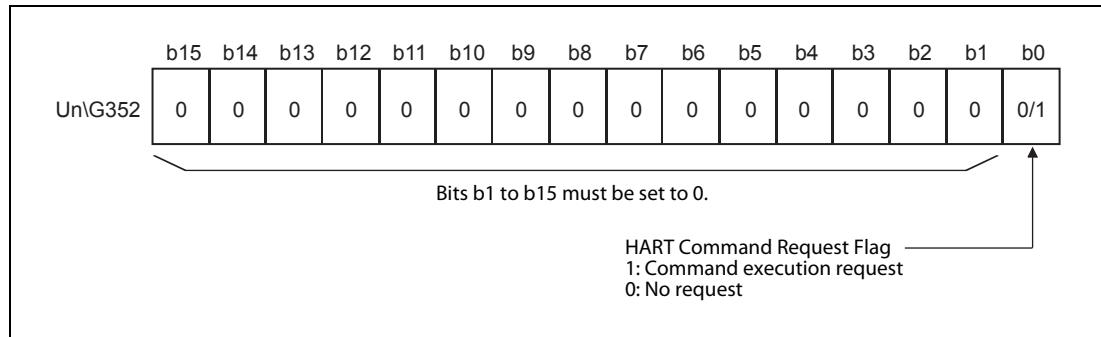

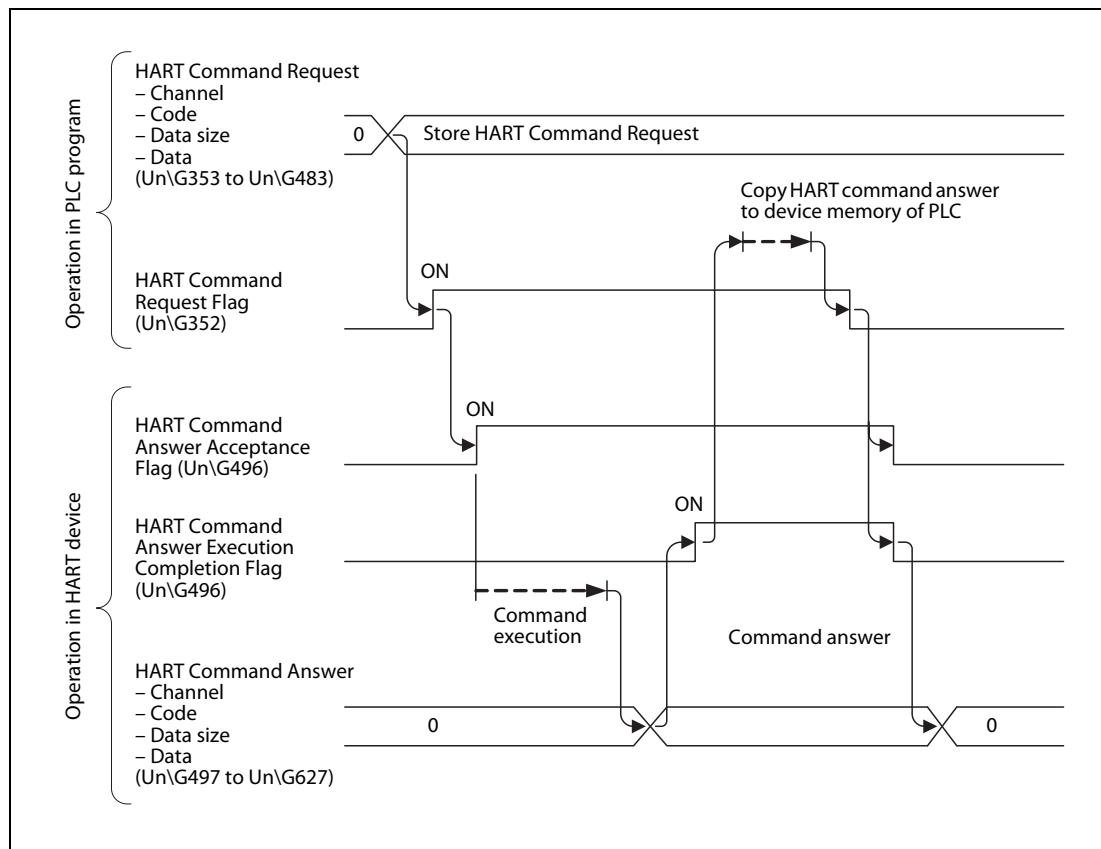

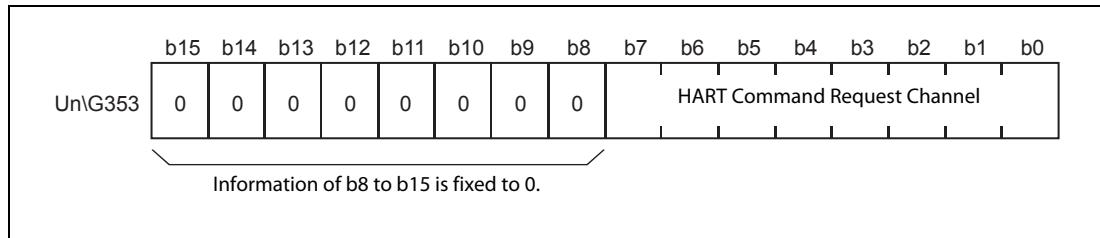

| 3.5.30 | HART Command Request (Un\G352 to Un\G483) .....                                  | 3-57 |

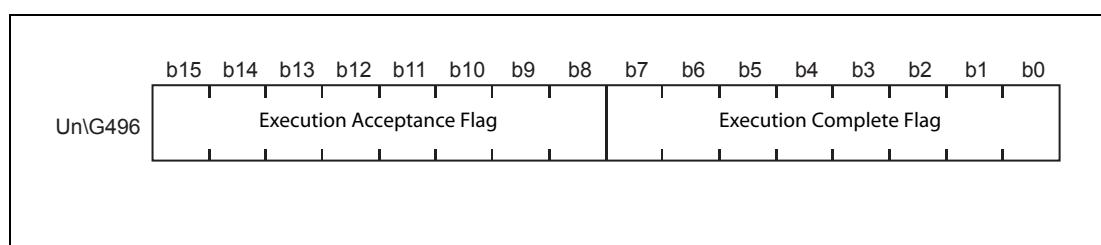

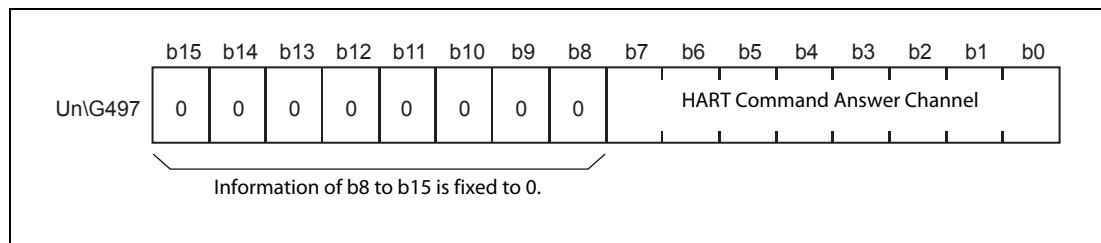

| 3.5.31 | HART Command Answer (Un\G496 to Un\G627) .....                                   | 3-59 |

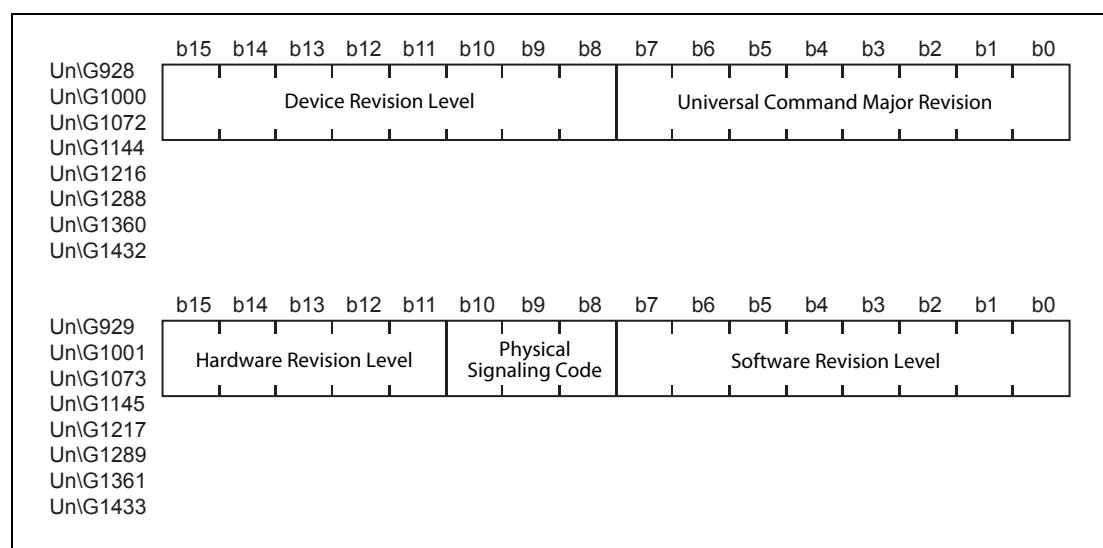

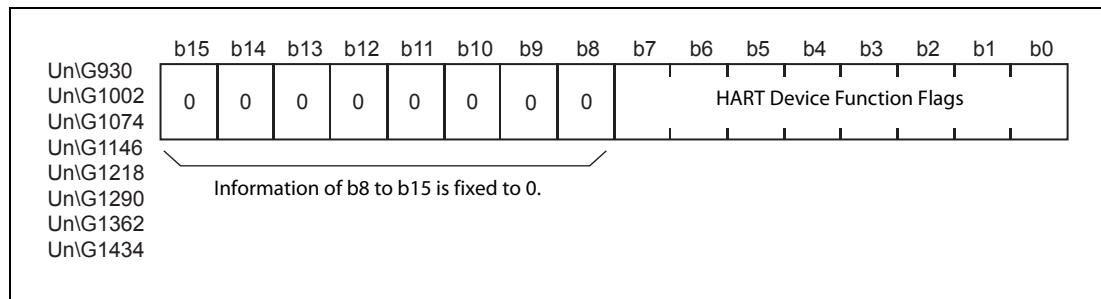

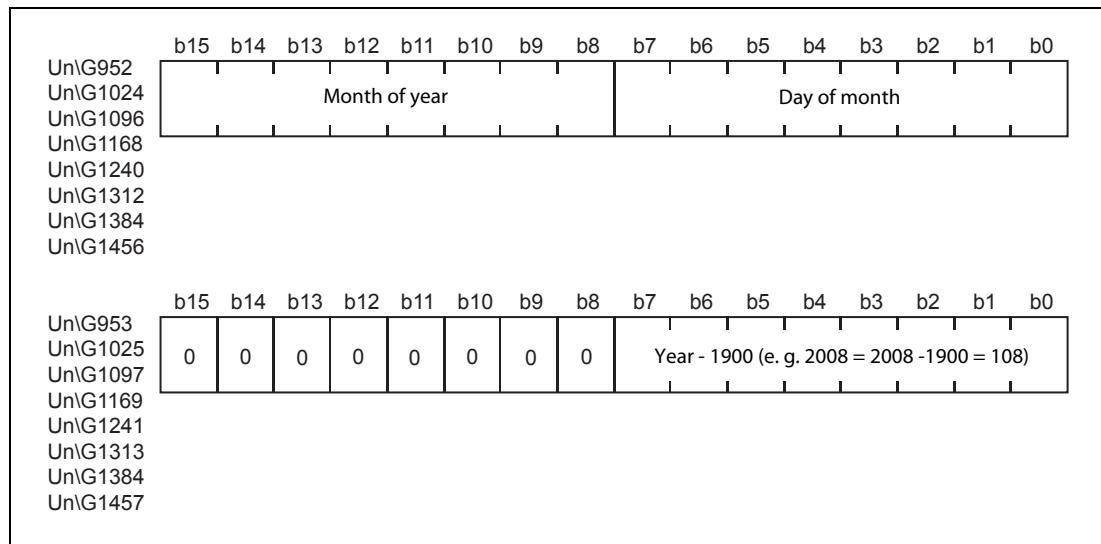

| 3.5.32 | Information about HART device (Un\G896 to Un\G966, Un\G968 to Un\G1038...) ..... | 3-60 |

## 4 Setup and Procedures before Operation

|       |                                                  |      |

|-------|--------------------------------------------------|------|

| 4.1   | Handling Precautions.....                        | 4-1  |

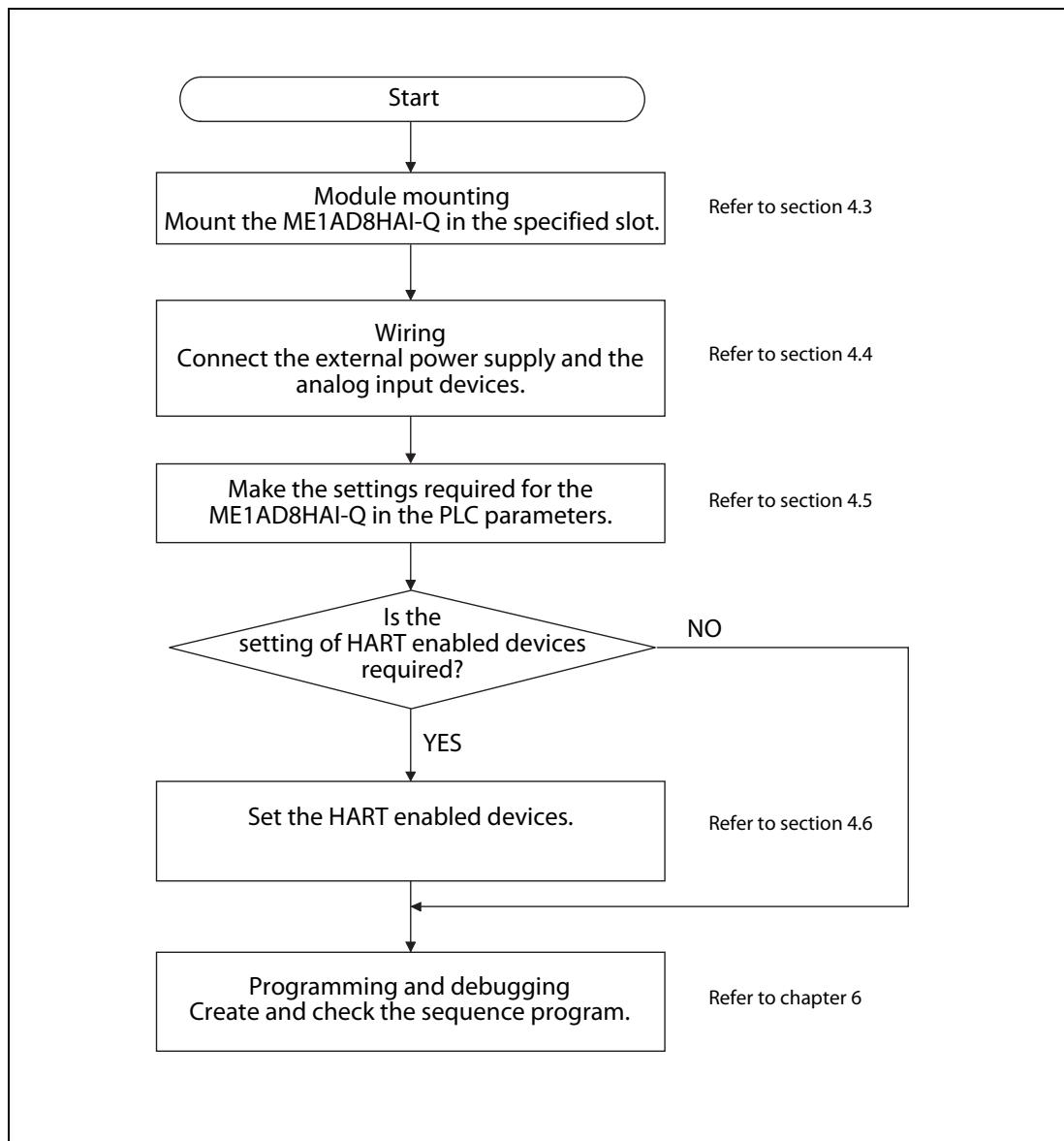

| 4.2   | Setup and Procedures before Operation .....      | 4-2  |

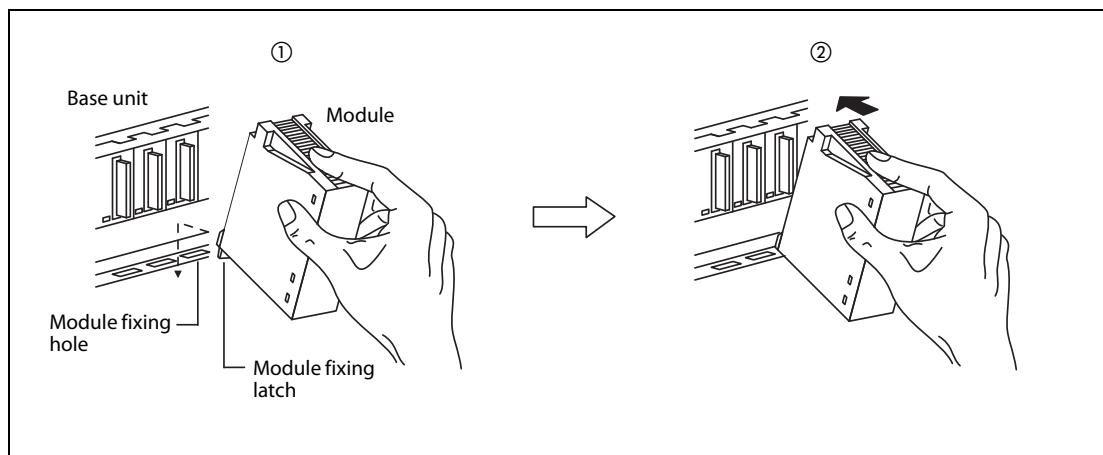

| 4.3   | Installation of the Module .....                 | 4-3  |

| 4.4   | Wiring .....                                     | 4-4  |

| 4.4.1 | Wiring precautions .....                         | 4-4  |

| 4.4.2 | External wiring .....                            | 4-4  |

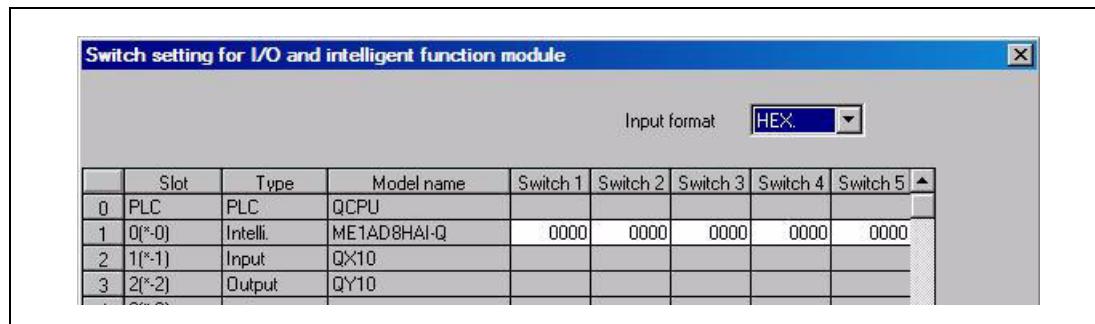

| 4.5   | PLC Parameter Setting.....                       | 4-9  |

| 4.5.1 | I/O assignment .....                             | 4-9  |

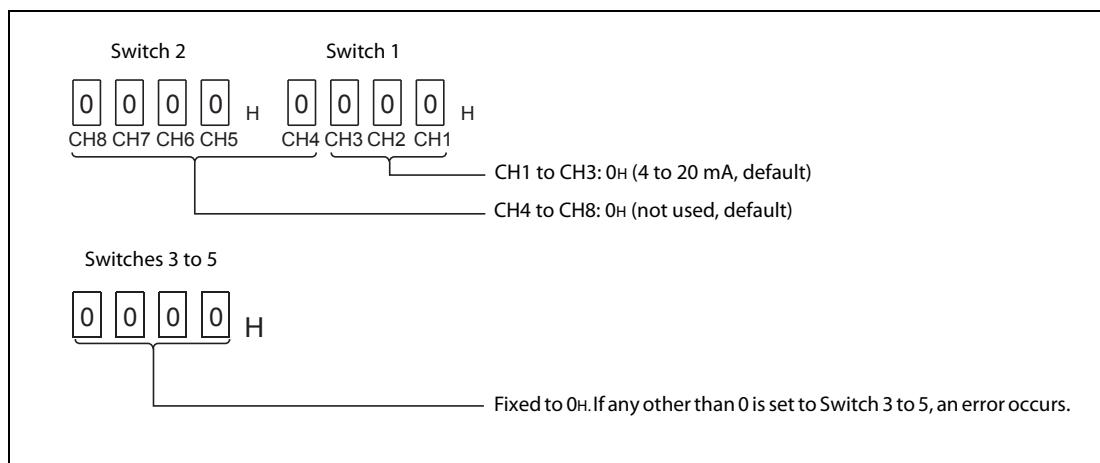

| 4.5.2 | Intelligent function module switch settings..... | 4-10 |

| 4.6   | Setting of the HART Devices .....                | 4-11 |

**5 Intelligent Function Utility (GX Works2)**

|     |                                                                   |     |

|-----|-------------------------------------------------------------------|-----|

| 5.1 | Addition of a new Module to the Project .....                     | 5-1 |

| 5.2 | Switch Setting.....                                               | 5-3 |

| 5.3 | Parameter Setting .....                                           | 5-5 |

| 5.4 | Auto Refresh Settings.....                                        | 5-7 |

| 5.5 | Writing the Intelligent Function Module Settings to the PLC ..... | 5-8 |

**6 Programming**

|       |                                                        |      |

|-------|--------------------------------------------------------|------|

| 6.1   | Programming Procedure .....                            | 6-1  |

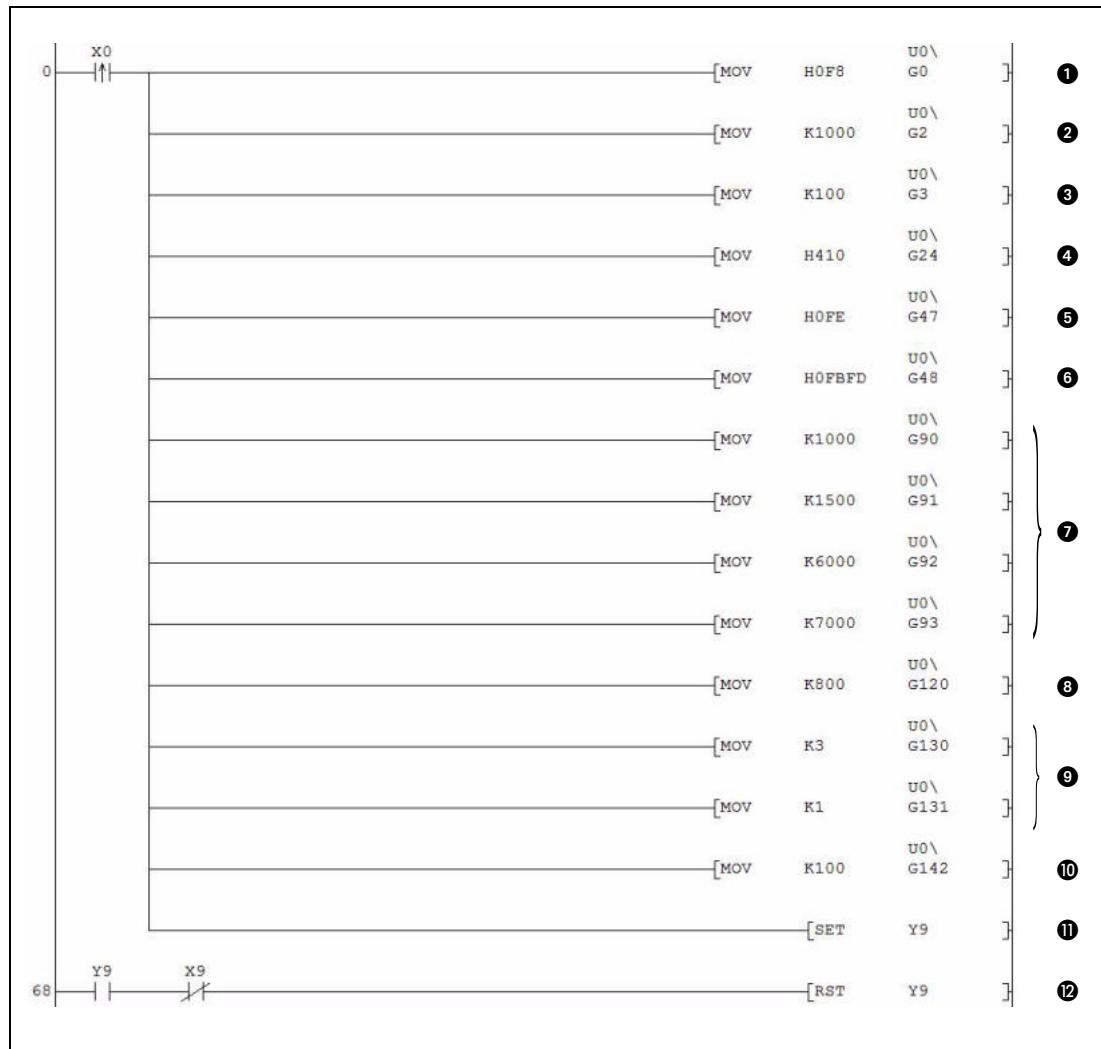

| 6.2   | Example 1: ME1AD8HAI-Q combined with PLC CPU.....      | 6-2  |

| 6.2.1 | Before creating a program .....                        | 6-3  |

| 6.2.2 | Program.....                                           | 6-4  |

| 6.3   | Example 2: ME1AD8HAI-Q used in Remote I/O Network..... | 6-9  |

| 6.3.1 | Before creating a program .....                        | 6-10 |

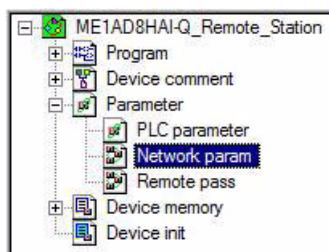

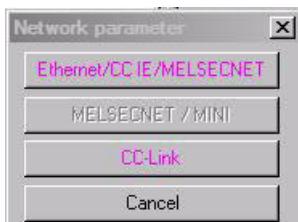

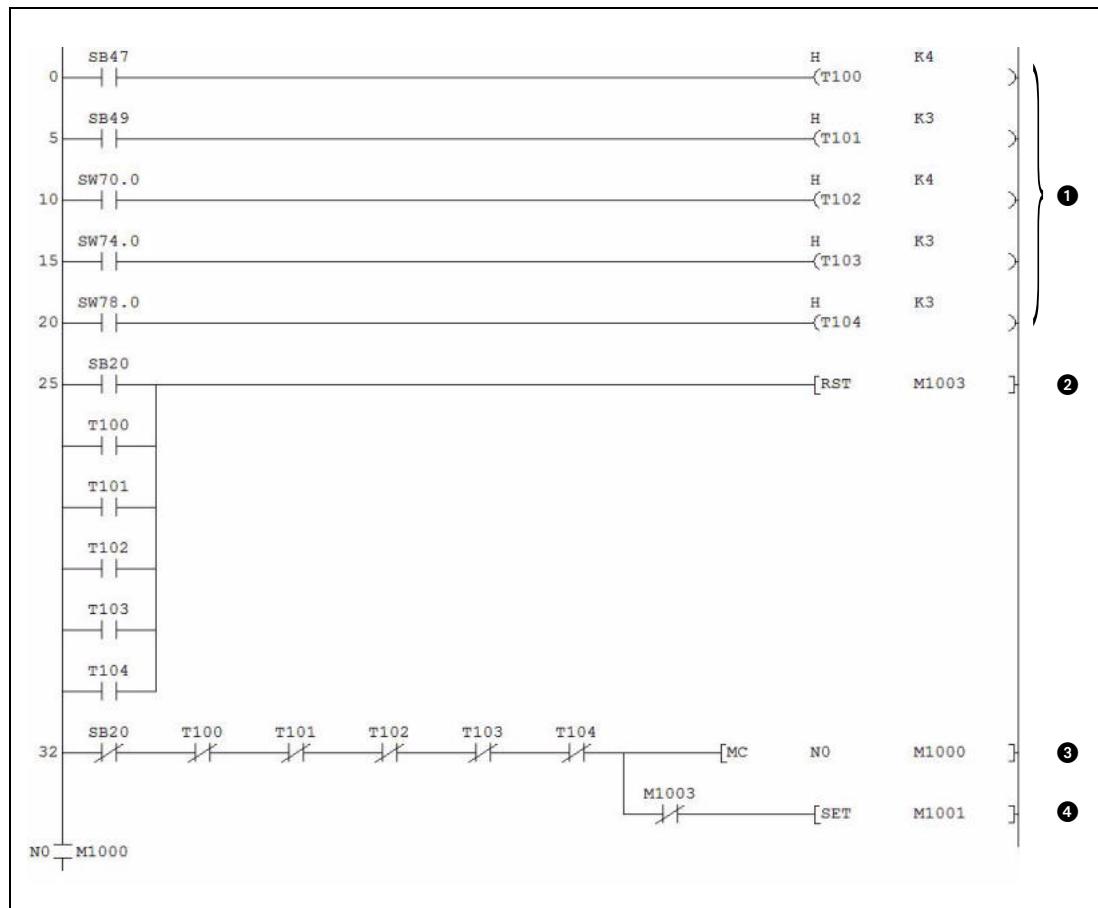

| 6.3.2 | Network Parameter and Program .....                    | 6-12 |

**7 Troubleshooting**

|       |                                                           |     |

|-------|-----------------------------------------------------------|-----|

| 7.1   | Error Code List.....                                      | 7-1 |

| 7.2   | Troubleshooting using the LEDs of the Module.....         | 7-3 |

| 7.2.1 | When the "RUN" LED is flashing or turned off .....        | 7-3 |

| 7.2.2 | When the "ERR." LED is on or flashing.....                | 7-3 |

| 7.2.3 | When the "ALM" LED is on or flashing .....                | 7-3 |

| 7.3   | When the digital output values cannot be read.....        | 7-4 |

| 7.3.1 | When A/D conversion completed flag does not turn ON ..... | 7-4 |

| 7.4   | Checking the Analog Input Module Status.....              | 7-5 |

**Index**

# 1 Overview

This User's Manual describes the specifications, handling and programming methods for the HART analog input module ME1AD8HAI-Q (hereinafter referred to as the ME1AD8HAI-Q) which is used with the CPU modules of the MELSEC System Q. The ME1AD8HAI-Q is exclusively used for current input.

## 1.1 Features

### **Multi-channel analog input is available.**

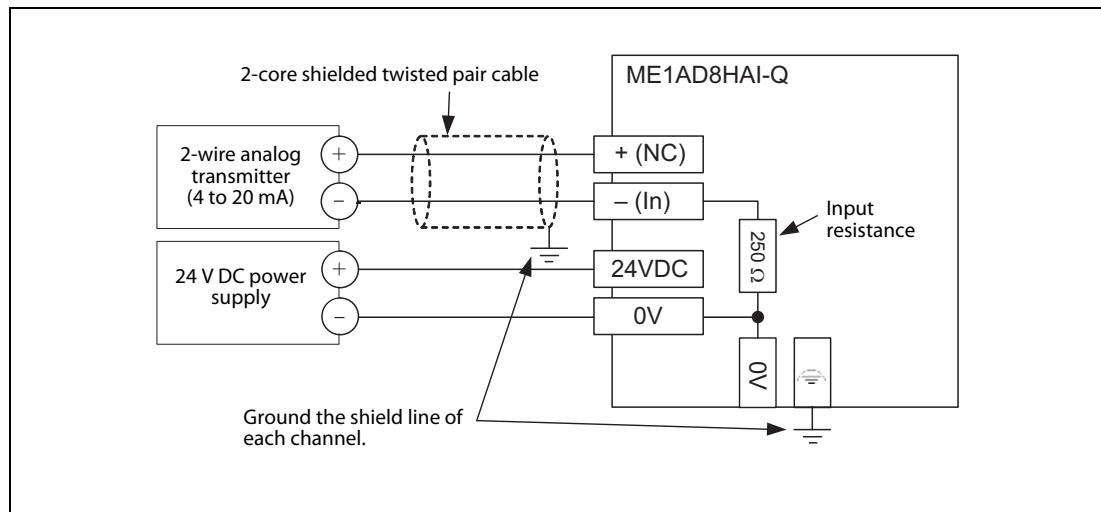

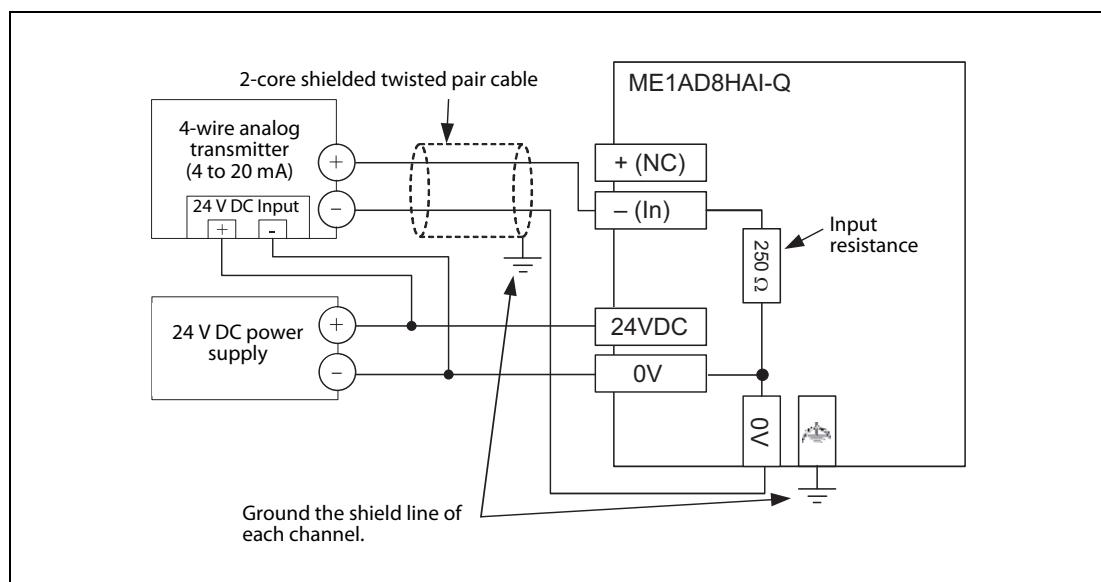

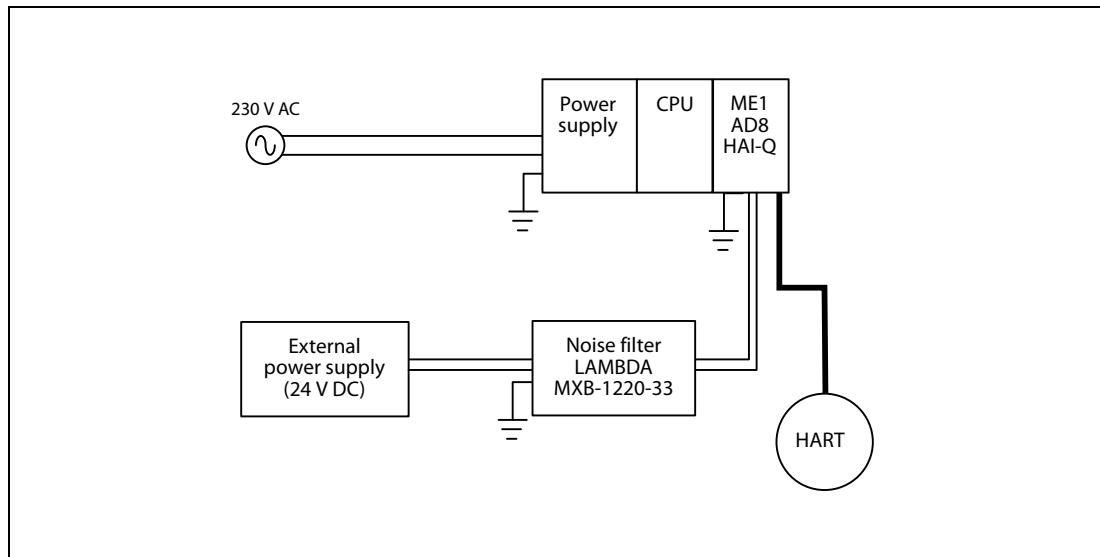

By using a single ME1AD8HAI-Q, analog current inputs of 8 points (8 channels) are available. Standard analog input devices with 4 to 20 mA or 0 to 20 mA range can be mixed with HART devices. The analog input range is selectable by the intelligent function module switch setting in GX(IEC) Developer. 2-wire or 4-wire analog transmitters can be connected.

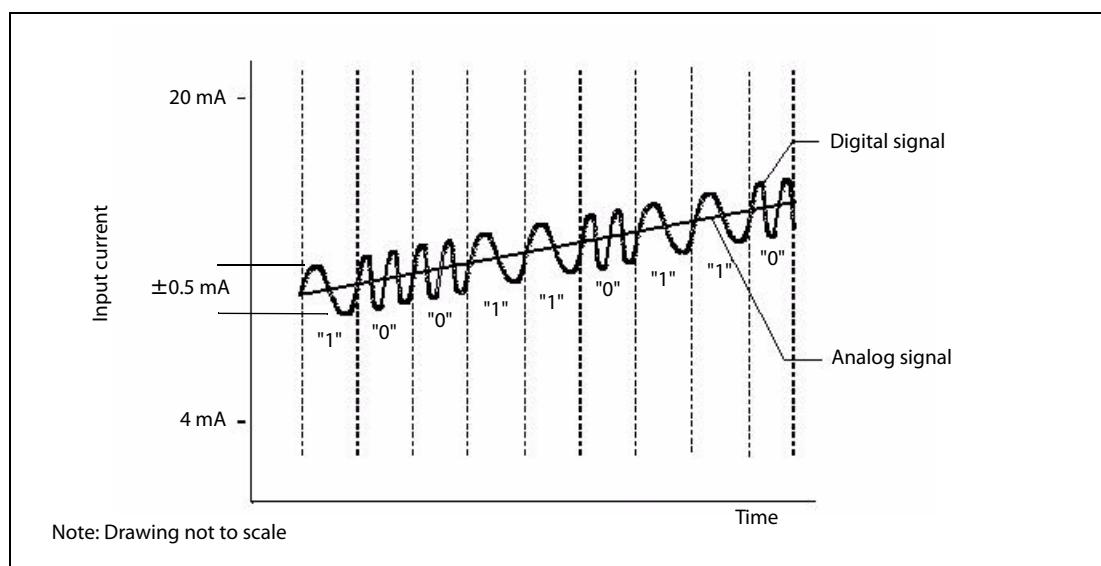

### **HART master function**

The ME1AD8HAI-Q can communicate with up to eight HART-enabled devices. (One HART device connected to each channel.) HART\* is a bi-directional industrial field communication protocol used to communicate between intelligent field instruments and host systems.

For this communication no additional wiring is required. Additional device information is communicated using a digital signal that is superimposed on the analog signal. The digital signal contains information from and to the device including device configuration or re-configuration, device status, diagnostics, additional measured or calculated values, etc.

The ME1AD8HAI-Q can operate as a HART master with protocol revision 6.

\* HART stands for **H**ighway **A**ddressable **R**emote **T**ransducer. For more information about the HART protocol please refer to section 3.3.6.

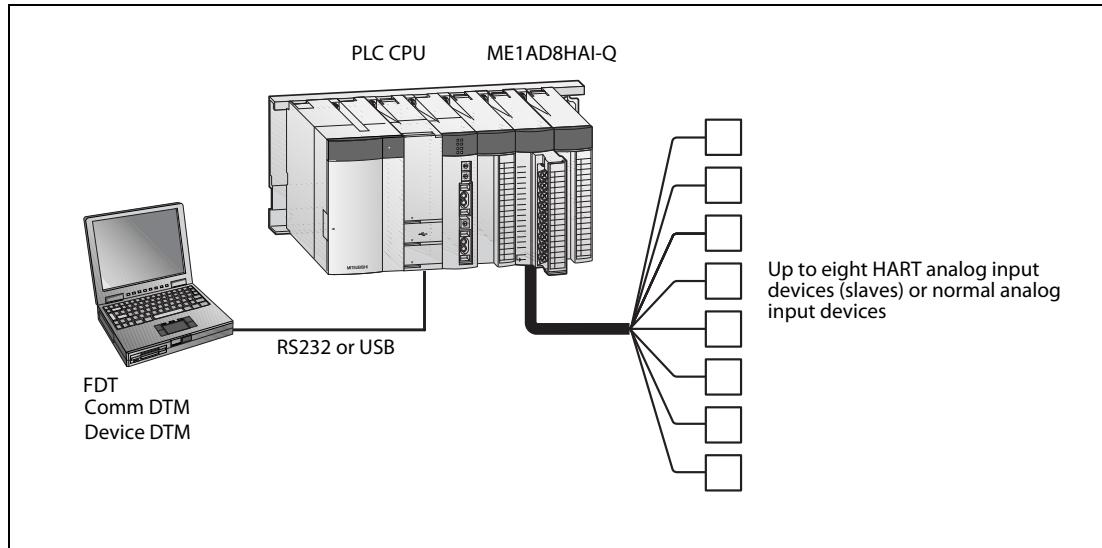

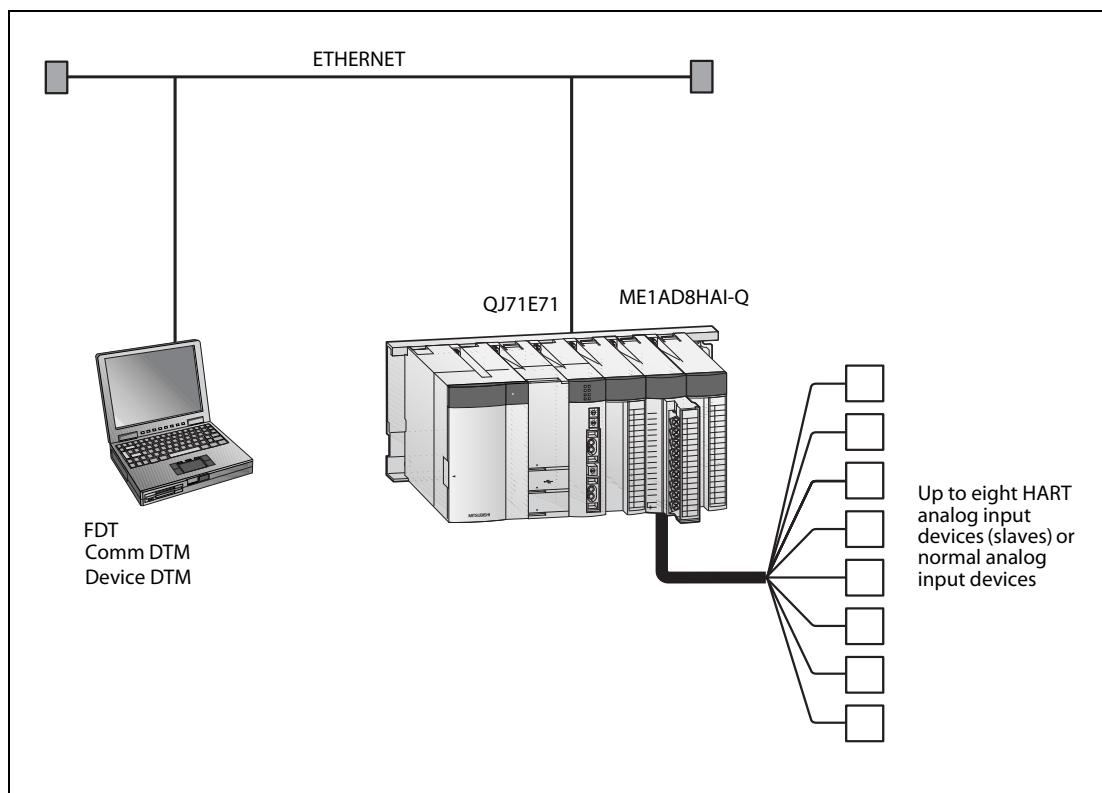

### **FDT/DTM function support**

The FDT/DTM can be used for setting and monitoring the HART devices. To use this function, the HART device must have DeviceDTM.

### **Power supply to 2-wire transmitter**

The ME1AD8HAI-Q supplies power to the connected 2-wire transmitters.

### **Module protection provided by short-circuit protection circuit**

If an excessive current flows into the module due to a short circuit of the wiring, the short-circuit protection circuit limits the current, thus protecting the module.

### **High accuracy**

The accuracy is as high as  $\pm 0.15\%$  over the specified operating temperature range for the MELSEC System Q.

### Changing the input range

The input range (4 to 20 mA or 0 to 20 mA) can easily be set from the GX (IEC) Developer.

### A/D conversion system

There are the following five A/D conversion systems.

- Sampling processing

Analog input values are converted into digital values one by one on a channel basis and the digital output value is triggered at every conversion.

- Averaging processing

- Time averaging

A/D conversion is averaged in terms of time on a channel basis and a digital average value is output.

- Count averaging

A/D conversion is averaged in terms of count on a channel basis and a digital average value is output.

- Move averaging

The specified number of digital output values measured per sampling time are averaged.

- Primary delay filter

A digital output value is smoothed according to the preset time constant.

Refer to section 3.3.1 for the details of the A/D conversion system.

### Input signal error detection function

A current outside the setting range can be detected.

### Warning output

There are the following two warning outputs.

- Process alarm

A warning is triggered if a digital output value falls outside the setting range.

- Rate alarm

A warning is triggered if the varying rate of a digital output value falls outside the preset varying rate range.

### Scaling function

A/D conversion values can be converted to percentage values (%) in the preset range and be loaded into the buffer memory. This function can reduce the time required for programming. (Refer to section 3.3.5)

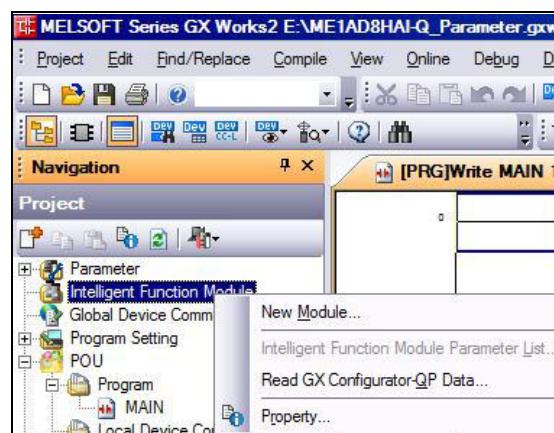

### Easy settings using the "Intelligent function utility"

The "Intelligent function utility" is not a required item, however, it is useful for on-screen setting of the intelligent function module parameters (initial setting/auto refresh setting).\*

\* The "Intelligent function utility" is supported by the ME1AD8HAI-Q if the first 5 digits of the serial number are "14102" or higher.

## 2 System Configuration

### 2.1 Applicable Systems

#### Applicable modules, base units, and No. of modules

- When mounted with a CPU module

The table below shows the CPU modules and base units applicable to the HART Analog Input Module ME1AD8HAI-Q and quantities for each CPU model.

Depending on the combination with other modules or the number of mounted modules, power supply capacity may be insufficient. Pay attention to the power supply capacity before mounting modules, and if the power supply capacity is insufficient, change the combination of the modules.

| Applicable CPU module       |                             | No. of<br>ME1AD8HAI-Q that<br>can be installed*1 | Base unit*2    |                     |  |

|-----------------------------|-----------------------------|--------------------------------------------------|----------------|---------------------|--|

| CPU type                    | CPU model                   |                                                  | Main base unit | Extension base unit |  |

| Programmable controller CPU | Basic model QCPU            | Q00JCPU                                          | Up to 16       | ●                   |  |

|                             |                             | Q00CPU                                           | Up to 24       |                     |  |

|                             |                             | Q01CPU                                           | ●              |                     |  |

|                             | High performance model QCPU | Q02CPU                                           | Up to 64       | ●                   |  |

|                             |                             | Q02HCPU                                          |                |                     |  |

|                             |                             | Q06HCPU                                          |                | ●                   |  |

|                             |                             | Q12HCPU                                          |                |                     |  |

|                             |                             | Q25HCPU                                          |                |                     |  |

|                             | Process CPU                 | Q02PHCPU                                         | Up to 64       | ●                   |  |

|                             |                             | Q06PHCPU                                         |                |                     |  |

|                             |                             | Q12PHCPU                                         |                | ●                   |  |

|                             |                             | Q25PHCPU                                         |                |                     |  |

|                             | Redundant CPU               | Q12PRHCPU                                        | Up to 53       | ○                   |  |

|                             |                             | Q25PRHCPU                                        |                |                     |  |

|                             | Universal model QCPU        | Q00UJCPU                                         | Up to 16       | ●                   |  |

|                             |                             | Q00UCPU                                          | Up to 24       |                     |  |

|                             |                             | Q01UCPU                                          |                |                     |  |

|                             |                             | Q02UCPU                                          | Up to 36       |                     |  |

|                             |                             | Q□UD(E)CPU                                       | Up to 64       |                     |  |

|                             |                             | Q50UDEHCPU                                       |                |                     |  |

|                             |                             | Q100UDEHCPU                                      |                |                     |  |

|                             | Safety CPU                  | QS001CPU                                         | —              | ○                   |  |

| C Controller module         |                             | Q06CCPU-V-H01                                    | Up to 64       | ●                   |  |

|                             |                             | Q06CCPU-V                                        |                |                     |  |

|                             |                             | Q06CCPU-V-B                                      |                |                     |  |

|                             |                             | Q12DCCPU-V                                       |                |                     |  |

**Tab. 2-1:** Applicable base units and number of mountable modules

● : Applicable, ○: N/A

\*1 Limited within the range of I/O points for the CPU module.

\*2 Can be installed to any I/O slot of a base unit.

#### NOTE

A ME1AD8HAI-Q can not be installed at the main base in a redundant system with QnPRHCPU.

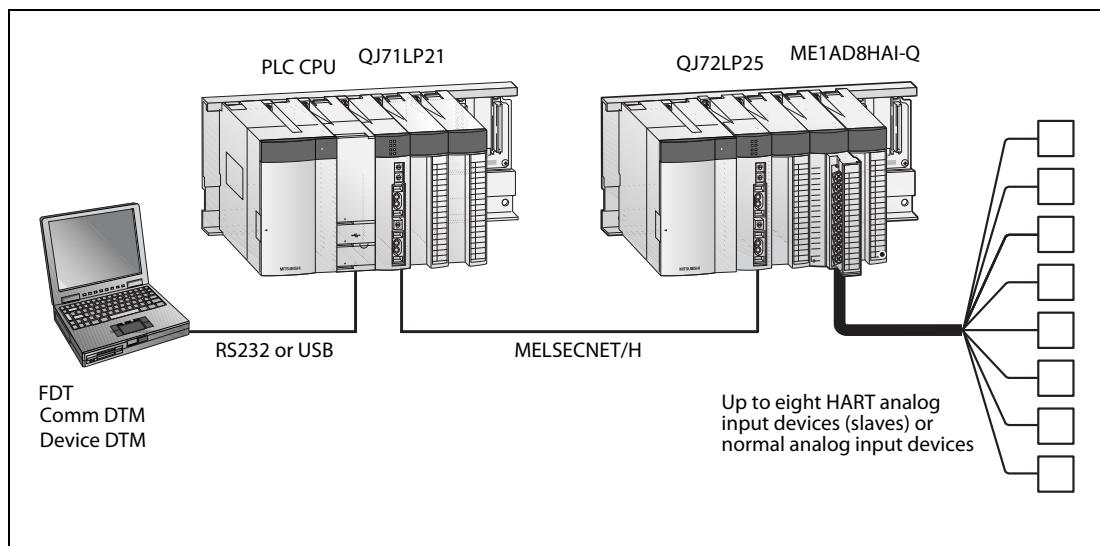

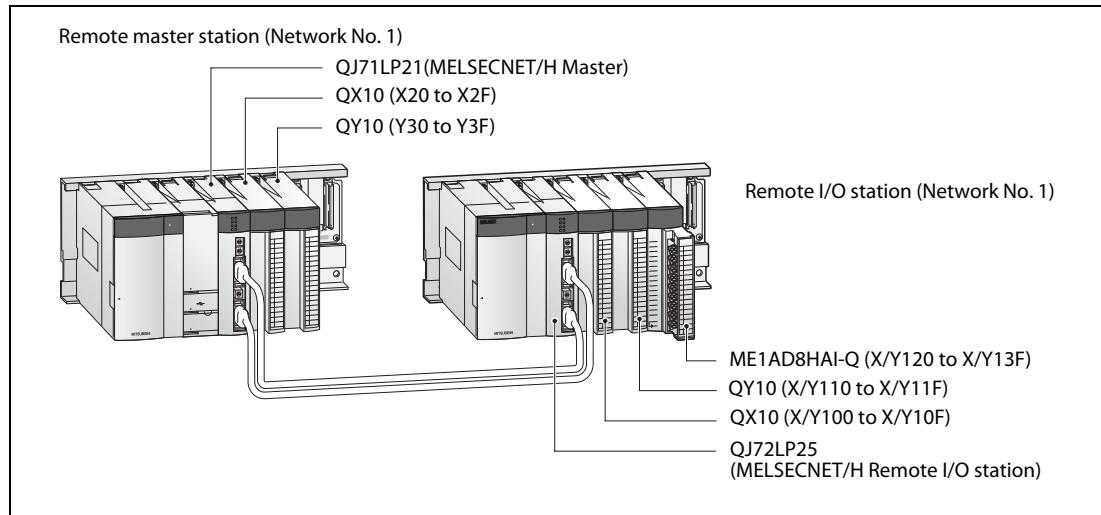

- Mounting to a MELSECNET/H remote I/O station

The table below shows the network modules and base units applicable to the analog input module ME1AD8HAI-Q and quantities for each network module model.

Depending on the combination with other modules or the number of mounted modules, power supply capacity may be insufficient. Pay attention to the power supply capacity before mounting modules, and if the power supply capacity is insufficient, change the combination of the modules.

| Applicable network module | No. of ME1AD8HAI-Q that can be installed <sup>*1</sup> | Base unit <sup>*2</sup>              |                                           |

|---------------------------|--------------------------------------------------------|--------------------------------------|-------------------------------------------|

|                           |                                                        | Main base unit of remote I/O station | Extension base unit of remote I/O station |

| QJ72LP25-25               | Up to 64                                               | ●                                    | ●                                         |

| QJ72LP25G                 |                                                        |                                      |                                           |

| QJ72LP25GE                |                                                        |                                      |                                           |

| QJ72BR15                  |                                                        |                                      |                                           |

**Tab. 2-2:** Applicable base units and number of mountable modules in a MELSECNET/H remote I/O station

● : Applicable, ○: N/A

\*1 Limited within the range of I/O points for the network module.

\*2 Can be installed to any I/O slot of a base unit.

**NOTE**

The Basic model QCPU or C Controller module cannot create the MELSECNET/H remote I/O network.

### Support of the multiple CPU system

The function version of the HART analog input module supports the multiple CPU system. When using the ME1AD8HAI-Q in a multiple CPU system, refer to the following manual first.

- QCPU User's Manual (Multiple CPU System)

### ● Intelligent function module parameters

Write intelligent function module parameters to only the control CPU of the ME1AD8HAI-Q.

### Compatibility with online module change

The ME1AD8HAI-Q does not support online module change.

### Supported software packages

For setting the PLC parameters for a system containing the ME1AD8HAI-Q and programming, the software packages GX Developer, GX IEC Developer and GX Works2 can be used.

In addition, the Intelligent Function Utility of GX Works2 can be used to set the intelligent function module parameters (initial settings/auto refresh settings) of the ME1AD8HAI-Q.

Depending on the CPU module used, a certain version of the software is needed since newly CPU modules are not supported by previous versions.

**NOTE**

Please check whether the mounted CPU module is supported or not by your version of the programming software.

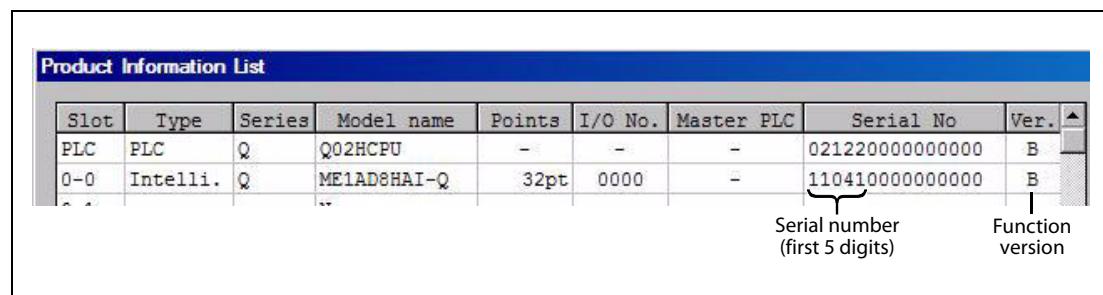

## 2.2 How to Check the Function Version and Serial No. of the Modules

Using the programming software GX Developer, GX IEC Developer or GX Works2, the serial No. and the function version can be checked while the PLC is operating.

From the **Diagnostics** menu select **System Monitor** and then select **Product Inf. List**.

The screenshot shows a software interface titled 'Product Information List'. It displays a table with the following data:

| Slot | Type     | Series | Model name  | Points | I/O No. | Master PLC | Serial No        | Ver. |

|------|----------|--------|-------------|--------|---------|------------|------------------|------|

| PLC  | PLC      | Q      | Q02HCPU     | -      | -       | -          | 0212200000000000 | B    |

| 0-0  | Intelli. | Q      | ME1AD8HAI-Q | 32pt   | 0000    | -          | 1104100000000000 | B    |

Annotations below the table:

- A bracket under the 'Serial No' column is labeled 'Serial number (first 5 digits)'

- A bracket under the 'Ver.' column is labeled 'Function version'

**Fig. 2-1:** Product Information List for a PLC with a ME1AD8HAI-Q

**NOTE**

The serial number displayed on the product information screen of GX Developer, GX IEC Developer or GX Works2 describes the function information of the product. The function information of the product is updated when a new function is added.

# 3 Detailed Description of the Module

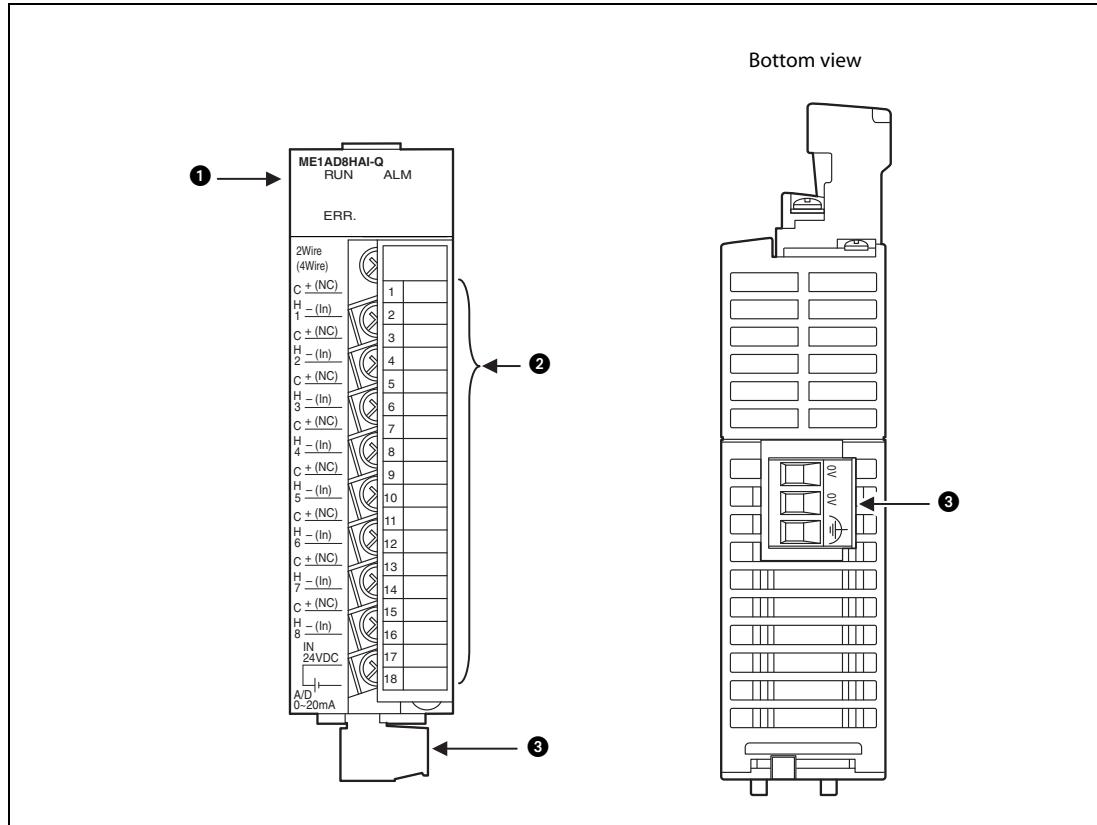

## 3.1 Part Names

This section explains the names of the components for the ME1AD8HAI-Q.

**Fig. 3-1:** Names of parts

| No. | Name                      | Description                                                                                                                                                                                                |

|-----|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ①   | RUN                       | Displays the operating status of the ME1AD8HAI-Q.<br>On: Normal operation<br>Flashing: Intelligent function module setting switch 4 is not set to "0".<br>Off: A watchdog timer error has occurred.        |

|     | ERR.                      | Displays the error status of the ME1AD8HAI-Q.<br>On: Operation error (HART communication error etc.)<br>Flashing: Intelligent function module setting switch 5 is not set to "0".<br>Off: Normal operation |

|     | ALM                       | Indicates the warning status of the ME1AD8HAI-Q.<br>On: An alarm (process alarm etc.) has occurred.<br>Flashing: An input signal error has occurred.<br>Off: Normal operation                              |

| ②   | Detachable terminal block | Used for connection of the HART input devices (slaves), analog input devices and external power supply.                                                                                                    |

| ③   | 0V/FG connector           | Used for FG connection and for connection with the '-' (minus) terminal of 4 wire devices.                                                                                                                 |

**Tab. 3-1:** Description of the LEDs and the terminal blocks of the ME1AD8HAI-Q

### NOTE

When two or more errors have occurred, the latest error found by the HART analog input module is indicated with the LED.

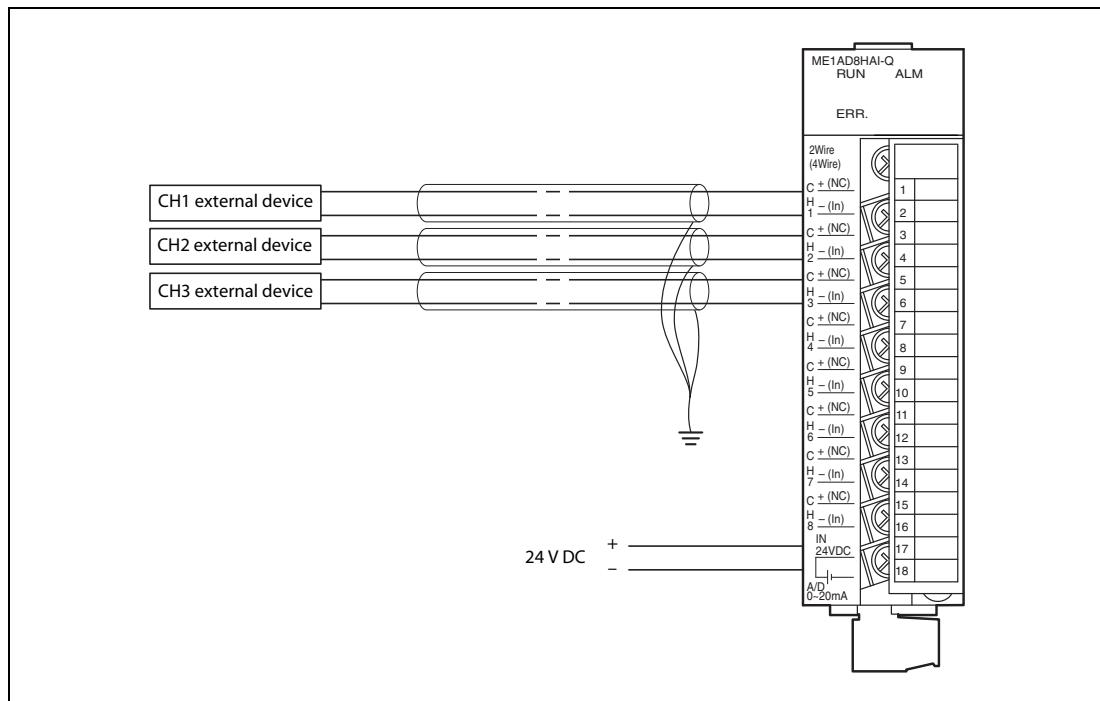

### 3.1.1 Signal Layout of the Terminal Block

| Terminal No. | Signal name           |         |

|--------------|-----------------------|---------|

| 1            | CH1                   | + (NC)  |

| 2            |                       | - (In)  |

| 3            | CH2                   | + (NC)  |

| 4            |                       | - (In)  |

| 5            | CH3                   | + (NC)  |

| 6            |                       | - (In)  |

| 7            | CH4                   | + (NC)  |

| 8            |                       | - (In)  |

| 9            | CH5                   | + (NC)  |

| 10           |                       | - (In)  |

| 11           | CH6                   | + (NC)  |

| 12           |                       | - (In)  |

| 13           | CH7                   | + (NC)  |

| 14           |                       | - (In)  |

| 15           | CH8                   | + (NC)  |

| 16           |                       | - (In)  |

| 17           | External power supply | + 24VDC |

| 18           |                       | 0 V     |

**Tab. 3-2:** Signal layout for the detachable terminal block of the ME1AD8HAI-Q

For the wiring of the HART analog input module ME1AD8HAI-Q please refer to section 4.4.

## 3.2 Specifications

The specifications for the ME1AD8HAI-Q are shown in the following table. For general specifications, refer to the operation manual for the CPU module being used.

| Item                                                      |                                                | Specifications                                                                                                                                                                                                                                                                                 |  |  |                    |                      |                    |            |            |          |            |  |          |

|-----------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--------------------|----------------------|--------------------|------------|------------|----------|------------|--|----------|

| Number of analog input points                             |                                                | 8 points (8 channels)                                                                                                                                                                                                                                                                          |  |  |                    |                      |                    |            |            |          |            |  |          |

| Analog input                                              | Current                                        | 0 to 20 mA DC<br>4 to 20 mA DC                                                                                                                                                                                                                                                                 |  |  |                    |                      |                    |            |            |          |            |  |          |

|                                                           | Absolute maximum input                         | ± 30 mA                                                                                                                                                                                                                                                                                        |  |  |                    |                      |                    |            |            |          |            |  |          |

|                                                           | Input resistance                               | 250 Ω                                                                                                                                                                                                                                                                                          |  |  |                    |                      |                    |            |            |          |            |  |          |

|                                                           | Short-circuit protection                       | Available                                                                                                                                                                                                                                                                                      |  |  |                    |                      |                    |            |            |          |            |  |          |

|                                                           | Primary filter                                 | 5 Hz (3 dB), HART signal is 1200 Hz with 1 mA P-P                                                                                                                                                                                                                                              |  |  |                    |                      |                    |            |            |          |            |  |          |

| Digital output                                            |                                                | 16-bit signed binary (-768 to 32767)                                                                                                                                                                                                                                                           |  |  |                    |                      |                    |            |            |          |            |  |          |

| I/O characteristics, maximum resolution                   |                                                | <table border="1"> <thead> <tr> <th>Analog input range</th> <th>Digital output value</th> <th>Maximum resolution</th> </tr> </thead> <tbody> <tr> <td>0 to 20 mA</td> <td>0 to 32000</td> <td>625.0 nA</td> </tr> <tr> <td>4 to 20 mA</td> <td></td> <td>500.0 nA</td> </tr> </tbody> </table> |  |  | Analog input range | Digital output value | Maximum resolution | 0 to 20 mA | 0 to 32000 | 625.0 nA | 4 to 20 mA |  | 500.0 nA |

| Analog input range                                        | Digital output value                           | Maximum resolution                                                                                                                                                                                                                                                                             |  |  |                    |                      |                    |            |            |          |            |  |          |

| 0 to 20 mA                                                | 0 to 32000                                     | 625.0 nA                                                                                                                                                                                                                                                                                       |  |  |                    |                      |                    |            |            |          |            |  |          |

| 4 to 20 mA                                                |                                                | 500.0 nA                                                                                                                                                                                                                                                                                       |  |  |                    |                      |                    |            |            |          |            |  |          |

|                                                           |                                                |                                                                                                                                                                                                                                                                                                |  |  |                    |                      |                    |            |            |          |            |  |          |

|                                                           |                                                |                                                                                                                                                                                                                                                                                                |  |  |                    |                      |                    |            |            |          |            |  |          |

| Accuracy <sup>*1</sup> (relative to digital output range) |                                                | ±0.15% (±48 digit <sup>*2</sup> )                                                                                                                                                                                                                                                              |  |  |                    |                      |                    |            |            |          |            |  |          |

| Cycle time                                                |                                                | 80 ms (Independent to the number of used channels)                                                                                                                                                                                                                                             |  |  |                    |                      |                    |            |            |          |            |  |          |

| Insulation method                                         | Between the I/O terminals and PLC power supply | Photo-coupler insulation                                                                                                                                                                                                                                                                       |  |  |                    |                      |                    |            |            |          |            |  |          |

|                                                           | Between analog input channels                  | Non-insulated                                                                                                                                                                                                                                                                                  |  |  |                    |                      |                    |            |            |          |            |  |          |

| HART modem                                                |                                                | FSK Physical Layer, multiplexed                                                                                                                                                                                                                                                                |  |  |                    |                      |                    |            |            |          |            |  |          |

|                                                           |                                                | – Protocol Revision 6 support                                                                                                                                                                                                                                                                  |  |  |                    |                      |                    |            |            |          |            |  |          |

| HART functions                                            |                                                | – 4 Process variables support (PV, SV, TV, QV)<br>– FDT/DTM support                                                                                                                                                                                                                            |  |  |                    |                      |                    |            |            |          |            |  |          |

| Number of I/O occupied points                             |                                                | 32 points (I/O assignment: Intelligent 32 points)                                                                                                                                                                                                                                              |  |  |                    |                      |                    |            |            |          |            |  |          |

| External wiring connection system                         |                                                | 18-points terminal block                                                                                                                                                                                                                                                                       |  |  |                    |                      |                    |            |            |          |            |  |          |

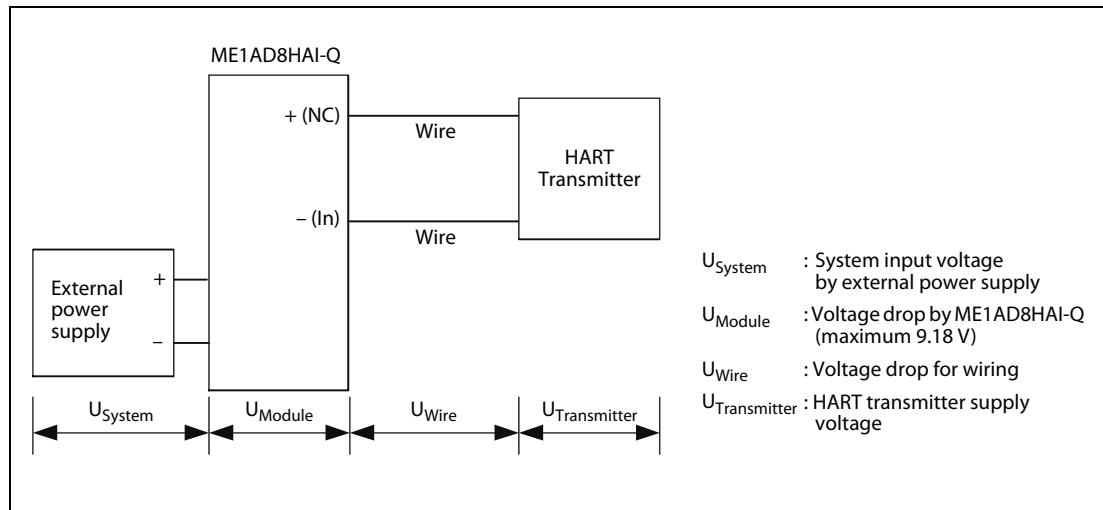

| Applicable wire size                                      |                                                | Refer to the HART specification for more details.<br>The external power supply voltage of the ME1AD8HAI-Q should be enough for correct operation of the analog transmitter. *3 *4                                                                                                              |  |  |                    |                      |                    |            |            |          |            |  |          |

| Applicable solderless terminals                           |                                                | R1.25-3 (Solderless terminals with sleeves cannot be used.)                                                                                                                                                                                                                                    |  |  |                    |                      |                    |            |            |          |            |  |          |

| External supply power                                     | Voltage                                        | 24 V DC (+20%, -15%); ripple, spike within 500mVp-p                                                                                                                                                                                                                                            |  |  |                    |                      |                    |            |            |          |            |  |          |

|                                                           | Current                                        | 0.3 A                                                                                                                                                                                                                                                                                          |  |  |                    |                      |                    |            |            |          |            |  |          |

|                                                           | Inrush current                                 | 5.5 A within 200 μs                                                                                                                                                                                                                                                                            |  |  |                    |                      |                    |            |            |          |            |  |          |

| Online module change                                      |                                                | Not supported                                                                                                                                                                                                                                                                                  |  |  |                    |                      |                    |            |            |          |            |  |          |

| Internal current consumption (5 VDC)                      |                                                | 0.32 A                                                                                                                                                                                                                                                                                         |  |  |                    |                      |                    |            |            |          |            |  |          |

| Weight                                                    |                                                | 0.19 kg                                                                                                                                                                                                                                                                                        |  |  |                    |                      |                    |            |            |          |            |  |          |

**Tab. 3-3:** Specifications of ME1AD8HAI-Q

\*1 ME1AD8HAI-Q needs to be powered on 30 minutes prior to operation for compliance to the specification (accuracy).

\*2 "digit" indicates a digital value.

\*3 Use case:

For distances up to 800 m, the wire size of 0.51 mm diameter with 115 nF/km cable capacitance and 36.7 Ω/km cable resistance can be applied.

\*4 Refer to the calculation example shown in section 4.4.2 (External wiring).

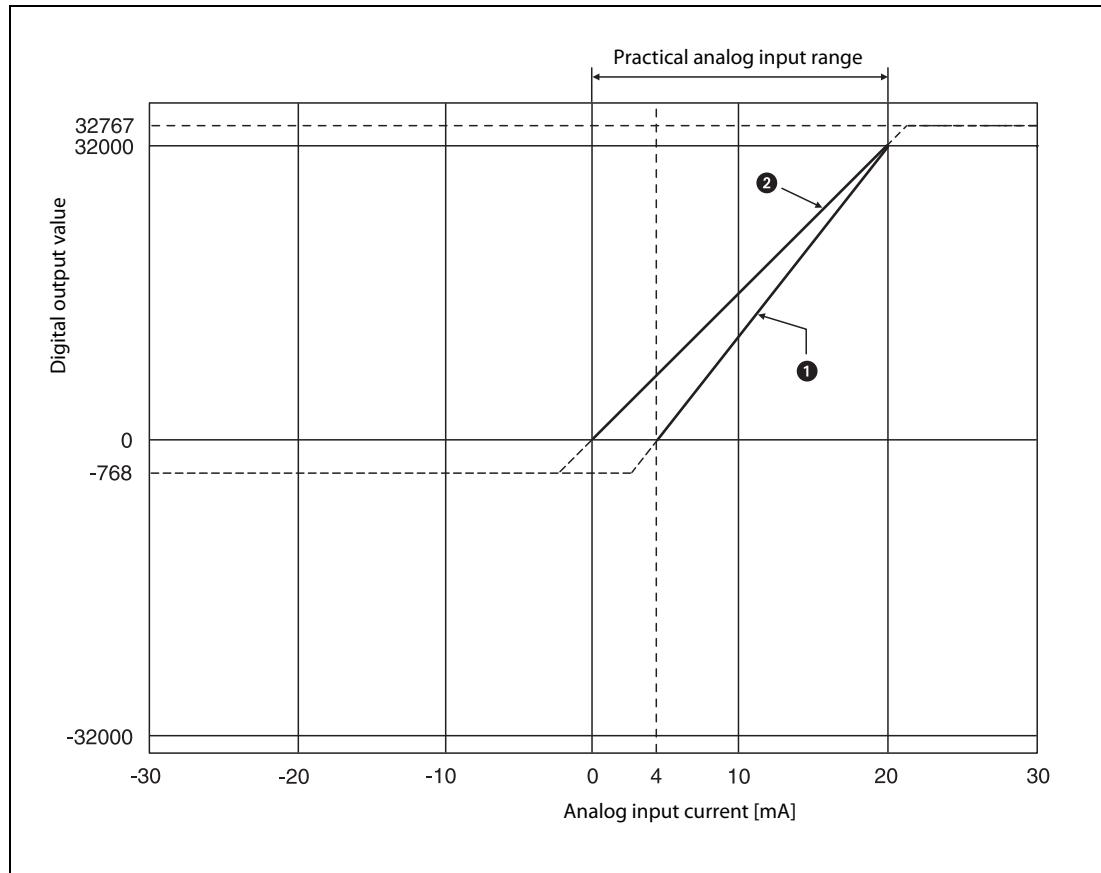

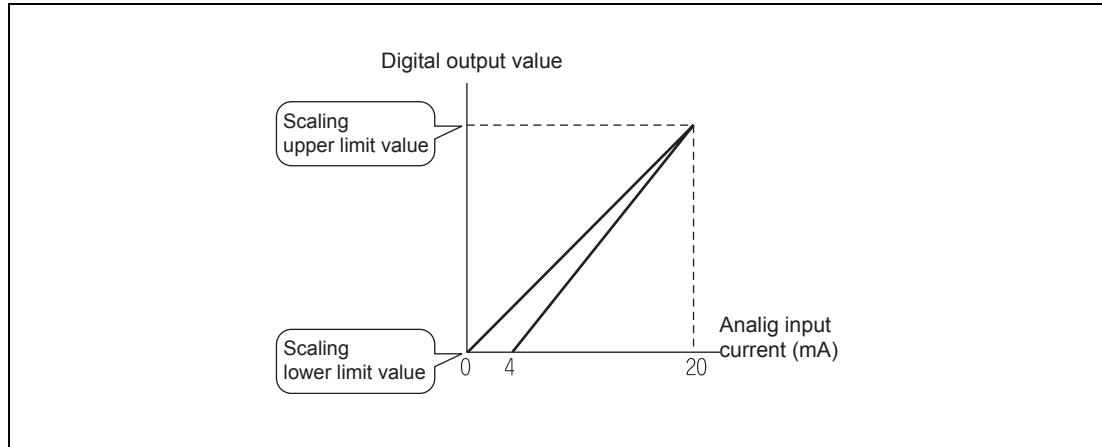

### 3.2.1 I/O conversion characteristic

The I/O conversion characteristic represents the angle formed by a straight line when the analog current signals from outside the programmable controller are converted to digital values.

**Fig. 3-2: Current input characteristics of the ME1AD8HAI-Q**

- ① Analog input range setting: 4 to 20 mA

- ② Analog input range setting: 0 to 20 mA

#### NOTES

- Choose the appropriate analog input range for each channel according to the specifications of the connected analog input device.

If these ranges are exceeded, the maximum resolution and accuracy may not fall within the performance specifications. (Avoid use shown by the dotted lines in the above table.)

- Do not input an analog input current of  $\pm 30$  mA or more. The input elements may be damaged.

- When an analog value that exceeds the range of the digital output value is entered, the digital output value will be fixed at the maximum or minimum value (32767 resp. -768).

### 3.2.2 Accuracy

The reference accuracy is the accuracy relative to the digital output range.

An accuracy of  $\pm 0.15\%$  is maintained over the whole operating temperature range of the MELSEC System Q (0 to  $+55^{\circ}\text{C}$ ).

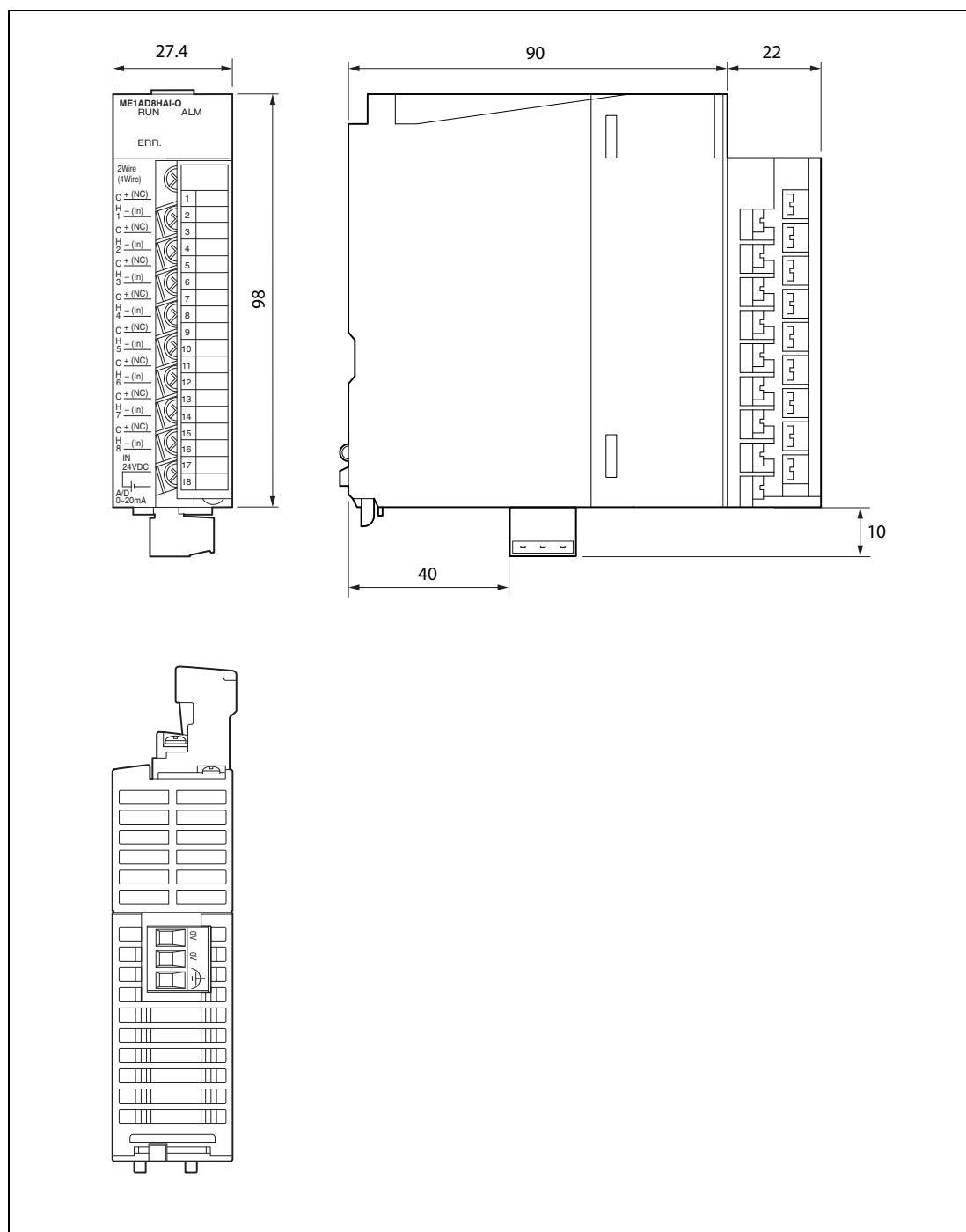

### 3.2.3 External Dimensions

**Fig. 3-3:** Dimensions of the ME1AD8HAI-Q

(Unit: mm)

### 3.3 Functions of the HART Analog Input Module

| Item                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reference section |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| A/D conversion enable/disable setting    | Specifies whether to enable or disable the A/D conversion for each channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Section 3.5.2     |

| A/D conversion method                    | <ul style="list-style-type: none"> <li>Sampling processing<br/>The A/D conversion for analog input values is performed successively for each channel, and the digital output value is output upon each conversion.</li> <li>Averaging processing <ul style="list-style-type: none"> <li>Time averaging<br/>A/D conversion is averaged in terms of time on a channel basis and a digital average value is output.</li> <li>Count averaging<br/>A/D conversion is averaged in terms of count on a channel basis and a digital average value is output.</li> <li>Move averaging<br/>The specified number of digital output values measured per cycle time are averaged.</li> </ul> </li> <li>Primary delay filter<br/>A digital output value is smoothed according to the preset time constant.</li> </ul> | Section 3.3.1     |

| Maximum and minimum values hold function | The maximum and minimum values of the digital output values are retained in the module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Section 3.3.2     |

| Input signal error detection function    | A current outside the setting range can be detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Section 3.3.3     |

| Warning output function                  | <ul style="list-style-type: none"> <li>Process alarm<br/>A warning is output if a digital output value falls outside the setting range.</li> <li>Rate alarm<br/>A warning is output if the varying rate of a digital output value falls outside the preset varying rate range.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Section 3.3.4     |

| Scaling function                         | Conversion of A/D conversion values to preset percentage values and loading into the buffer memory is available. Programming steps for the scaling can be eliminated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Section 3.3.5     |

| HART Master function                     | <ul style="list-style-type: none"> <li>HART communication support<br/>The ME1AD8HAI-Q can communicate with up to eight HART-enabled devices. (One HART device connected to each channel.) Communication occurs using standard instrumentation grade wire and using standard wiring and termination practices – no additional wiring is required.</li> <li>FDT/DTM function support<br/>Using a commercially available FDT, reading/writing the HART transmitter's parameters and monitoring the HART transmitter status are executable via the ME1AD8HAI-Q.</li> </ul>                                                                                                                                                                                                                                  | Section 3.3.6     |

**Tab. 3-4:** Functions of the ME1AD8HAI-Q

### 3.3.1 A/D conversion methods

#### Sampling processing

A/D conversion is performed successively for analog input values, and the converted digital output values are stored in the buffer memory.

#### Averaging processing

- Time averaging

A/D conversion is made for the preset period of time, the sum of values other than the maximum and minimum values is averaged, and the result is stored into the buffer memory.

The number of processing within the set time depends on the cycle time (Fixed to 80 ms independently to the number of channels enabled for A/D conversion) and can be calculated using the following formula:

$$\text{Number of processings [times]} = \text{Set time [ms]} / 80 \text{ [ms]}$$

Example:

Number of processings when setting 500 ms for the set time:  $500/80 = 6.25$  [times] → 6 [times]

- Count averaging

A/D conversion is made the preset number of times, the sum of values other than the maximum and minimum values is averaged, and the result is stored into the buffer memory.

The time required for the count-based average value to be stored into the buffer memory varies depends on the cycle time (Fixed to 80 ms independently to the number of channels enabled for A/D conversion) and can be calculated using the following formula:

$$\text{Processing time [ms]} = \text{Set count} \times 80 \text{ [ms]}$$

Example:

Processing time when setting 5 (times) for the average processing count:  $5 \times 80 = 400$  [ms]

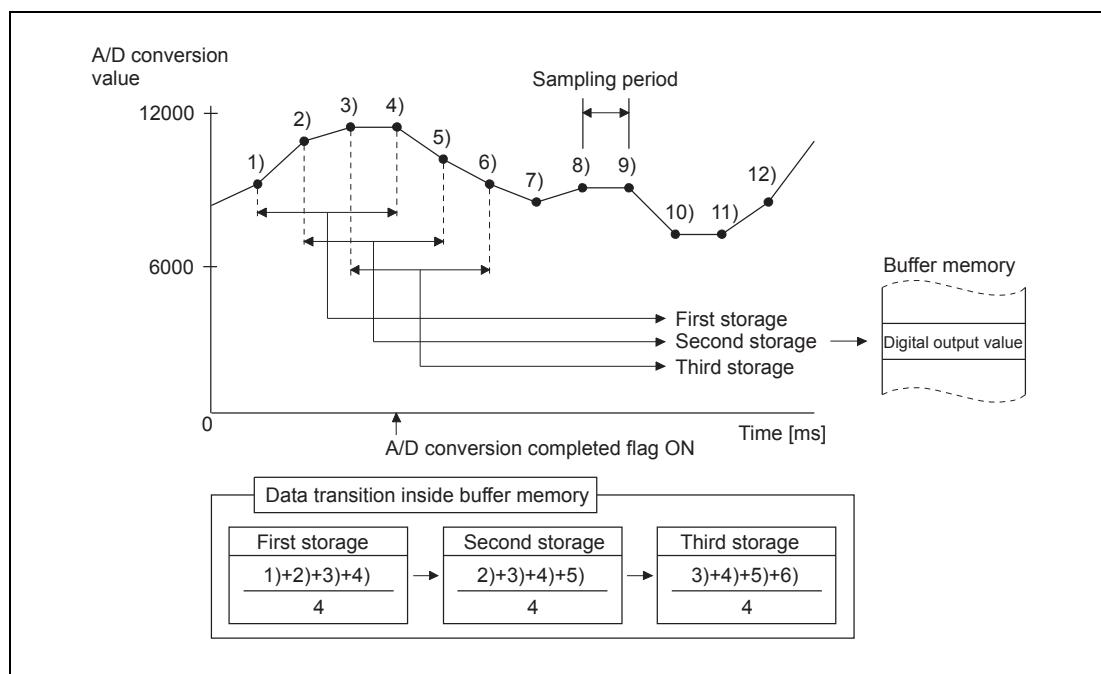

- Moving average

The specified count of digital output values imported per sampling period are averaged to find a value, which is then stored into the buffer memory. Since average processing is performed with data shifted per sampling, the most recent digital output value is obtainable.

Fig. 3-4: Moving average processing at the preset count of 4 times

### Primary delay filter

A digital value whose transient noise has been smoothed is output according to the preset time constant. The degree of smoothing varies with the time constant setting.

The relational expression of the time constant and digital output value is indicated below.

[If  $n = 1$ ]

$Y_n = 0$

[If  $n = 2$ ]\*

$$Y_n = Y_{n-1} + \frac{\Delta t}{\Delta t + TA} (Y_n - Y_{n-1})$$

[If  $n \geq 3$ ]

$$Y_n = Y_{n-1} + \frac{\Delta t}{\Delta t + TA} (Y_n - Y_{n-1})$$

$Y_n$ : Current digital output value

$Y_{n-1}$ : Immediately preceding digital output value

$n$ : Sampling count

$TA$ : Time constant [s]

$Y_n$ : Pre-smoothing digital output value

$Y_{n-1}$ : Immediately preceding presmoothing digital output value

$\Delta t$ : Cycle time (0.08)[s]

\*The A/D conversion completed flag turns ON when  $n \geq 2$ .

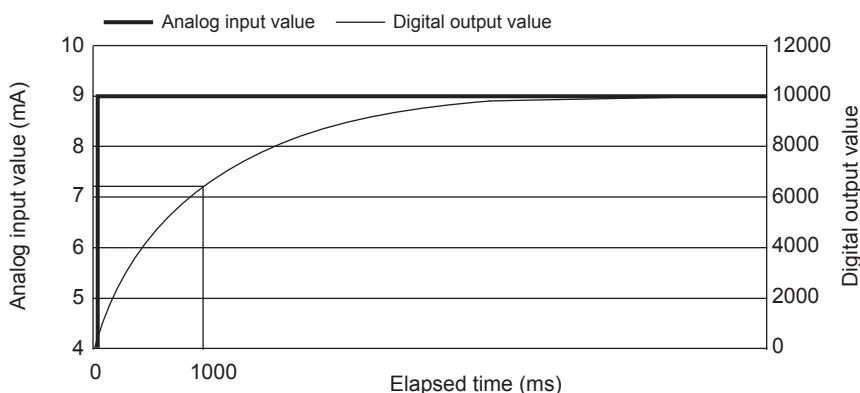

#### Example 1:

Digital output value when the analog input value varies from 4 to 10 mA

The variation of the digital output value at the time constant setting of 1000 ms (1 s) is as shown below. 1000 ms (1 s) after the analog input value has reached 10 mA, the digital output value reaches 63.2 % of the value attained when the sampling processing is selected.

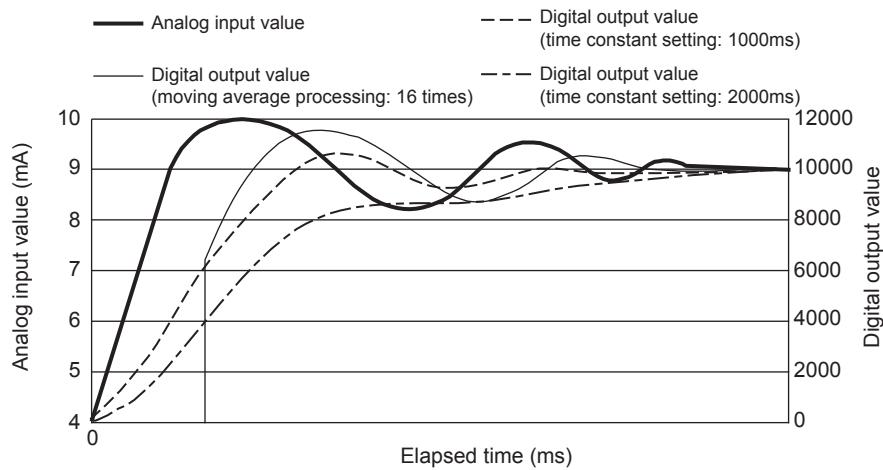

**Example 2:**

Digital output value when the variation of the analog input value has a ringing waveform

The variations of the digital output values at the time constant setting of 2000 ms (2 s), at the time constant setting of 1000 ms (1 s), and at the moving average processing of 16 times are as shown below.

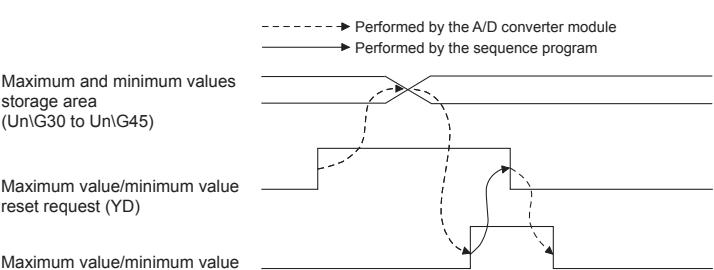

**3.3.2****Maximum and minimum values hold function**

The maximum and minimum values are held in the buffer memory channel by channel.

The maximum and minimum values are cleared to 0 when the maximum value/minimum value reset request (YD) or operating condition setting request (Y9) is turned ON, and new maximum and minimum values are stored when conversion is started.

Since the area for storing the maximum and minimum values can be rewritten with the sequence program, the maximum and minimum values within a specific period of time can be checked.

When the scaling function is enabled, values after scaling conversion are stored as the maximum and minimum values. For the scaling function, refer to section 3.3.5

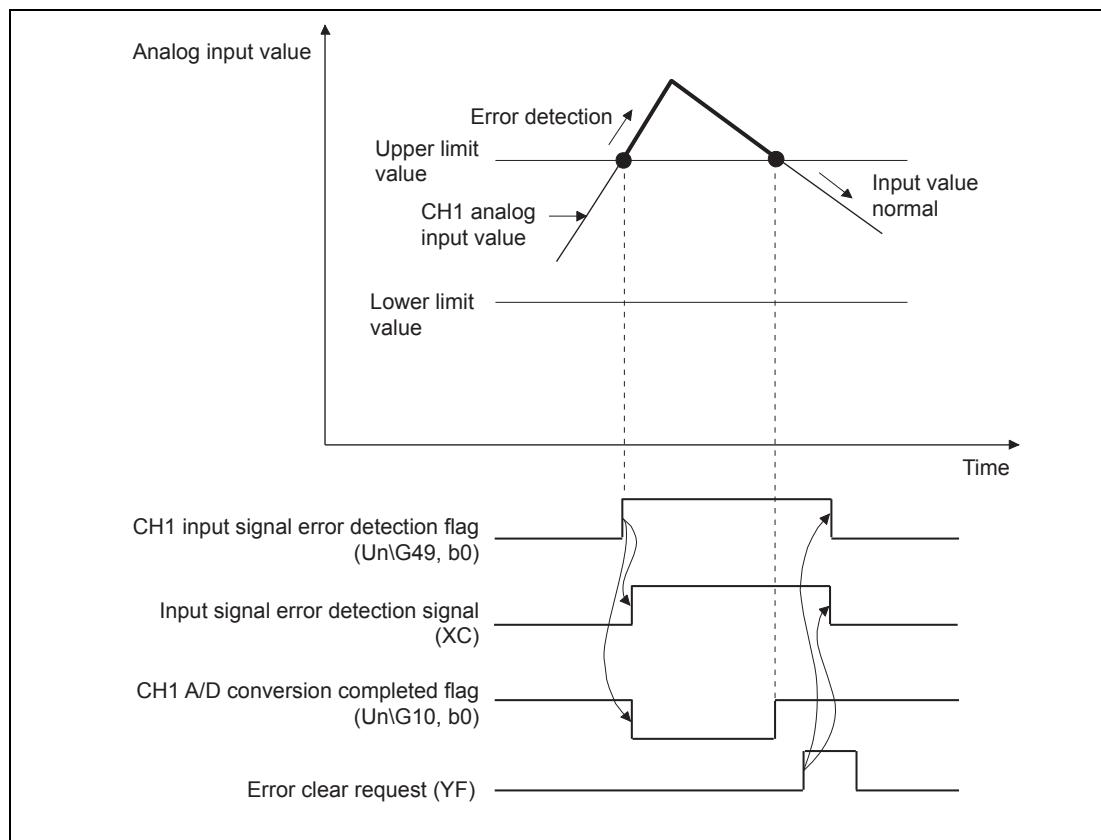

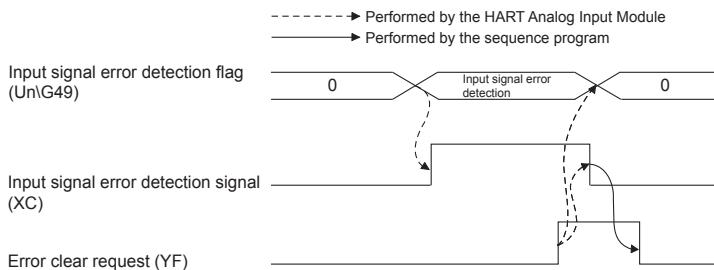

### 3.3.3 Input signal error detection function

If the input current rose to or above the input signal error detection upper limit value or fell to or below the lower limit value, the input signal error detection flag (Un\G49) and input signal error detection signal (XC) turn ON and the ALM LED flickers to indicate the error.

When the input signal error detection flag (Un\G49) turns ON for a channel, a digital output value immediately before the error detection is held for the channel, and the A/D conversion completed flag (Un\G10) of the corresponding channel turns OFF.

By bringing the analog input value within the setting range and then turning ON the error clear request (YF), the input signal error detection flag (Un\G49) and input signal error detection signal (XC) turn OFF.

When the analog input value returns to within the setting range, A/D conversion is resumed independently of whether the input signal error detection flag (Un\G49) and input signal error detection signal (XC) are reset or not, the A/D conversion completed flag (Un\G10) of the corresponding channel turns ON again after the first updating. (The ERR. LED remains flickering.)

**Fig. 3-5: Input signal error detection function**

This function is executed at every sampling processing. Perform the following procedure to use this function.

- Set the input signal error detection setting value for the corresponding channel.

- Enable the A/D conversion of the corresponding channel.

- Enable the input signal error detection of the corresponding channel.

- Turn ON the operating condition setting request (Y9).

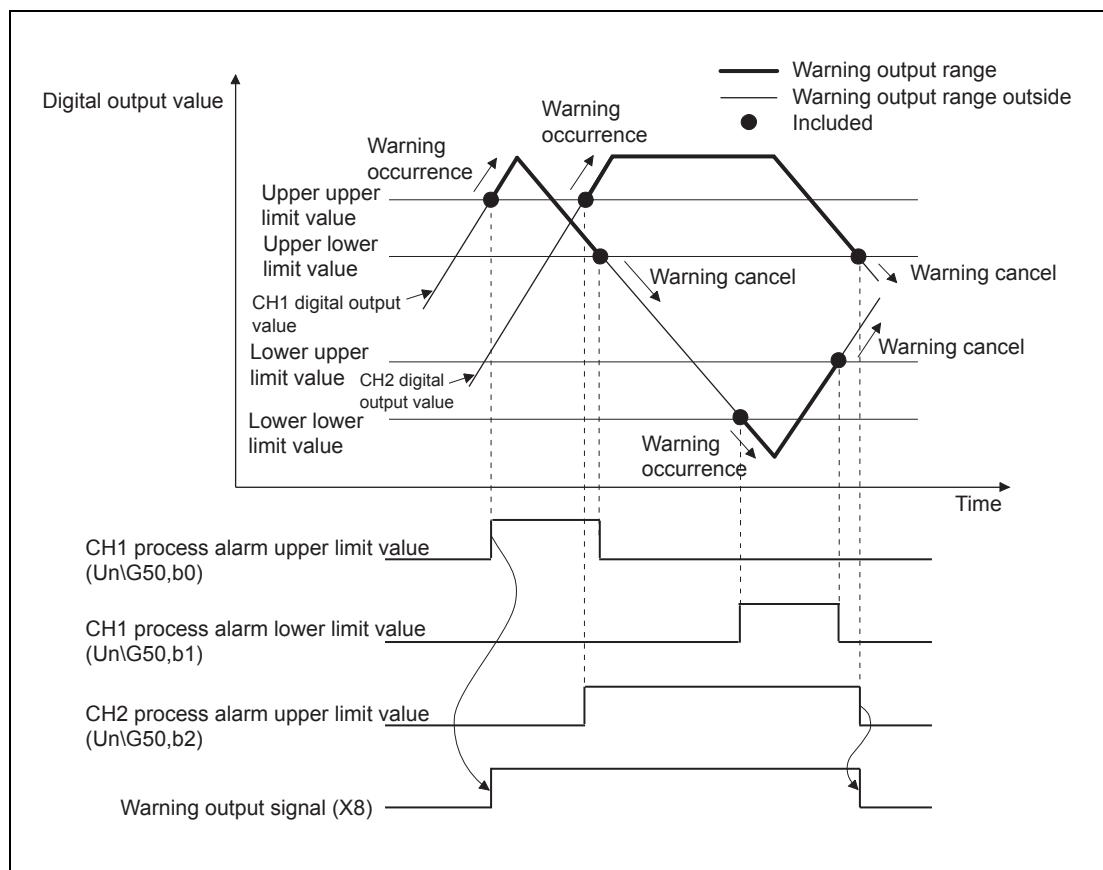

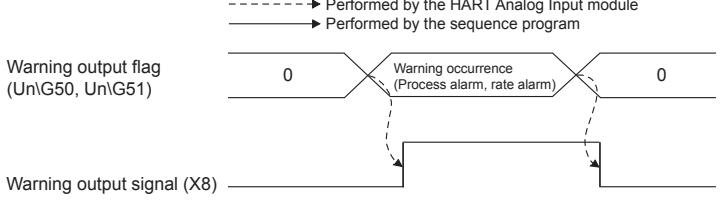

### 3.3.4 Warning output function

#### Process alarm

If the detected digital output value rose to or above the process alarm upper upper limit value or fell to or below the process alarm lower lower limit value and entered the warning output range zone, the warning output flag (process alarm)(Un\G50) and warning output signal (X8) turn ON and the ALM LED is lit to indicate the warning.

A warning will be output according to the following digital output values.

| Item                                                 | Digital value causing warning output |                                             |

|------------------------------------------------------|--------------------------------------|---------------------------------------------|

| Value set in scaling enable/disable setting (Un\G53) | 0: Disable                           | CH□ digital output value (Un\G11 to Un\G18) |

|                                                      | 1: Enable                            | CH□ scaling value (Un\G54 to Un\G61)        |

**Tab. 3-5:** The source for the warning depends on the setting in the buffer memory address Un\G53

The warning output signal (X8) turns OFF only when all channels return to within the setting range.

**Fig. 3-6:** Warning output function (process alarm)

When time or count averaging is specified, this function is executed at intervals of the preset averaging time or averaging count. When any other A/D conversion system (sampling processing, moving average, primary delay filter) is specified, this function is executed at intervals of the cycle time.

To use the scaling function, be sure to consider the scaling conversion before setting the CH□ process alarm upper/lower limit value.

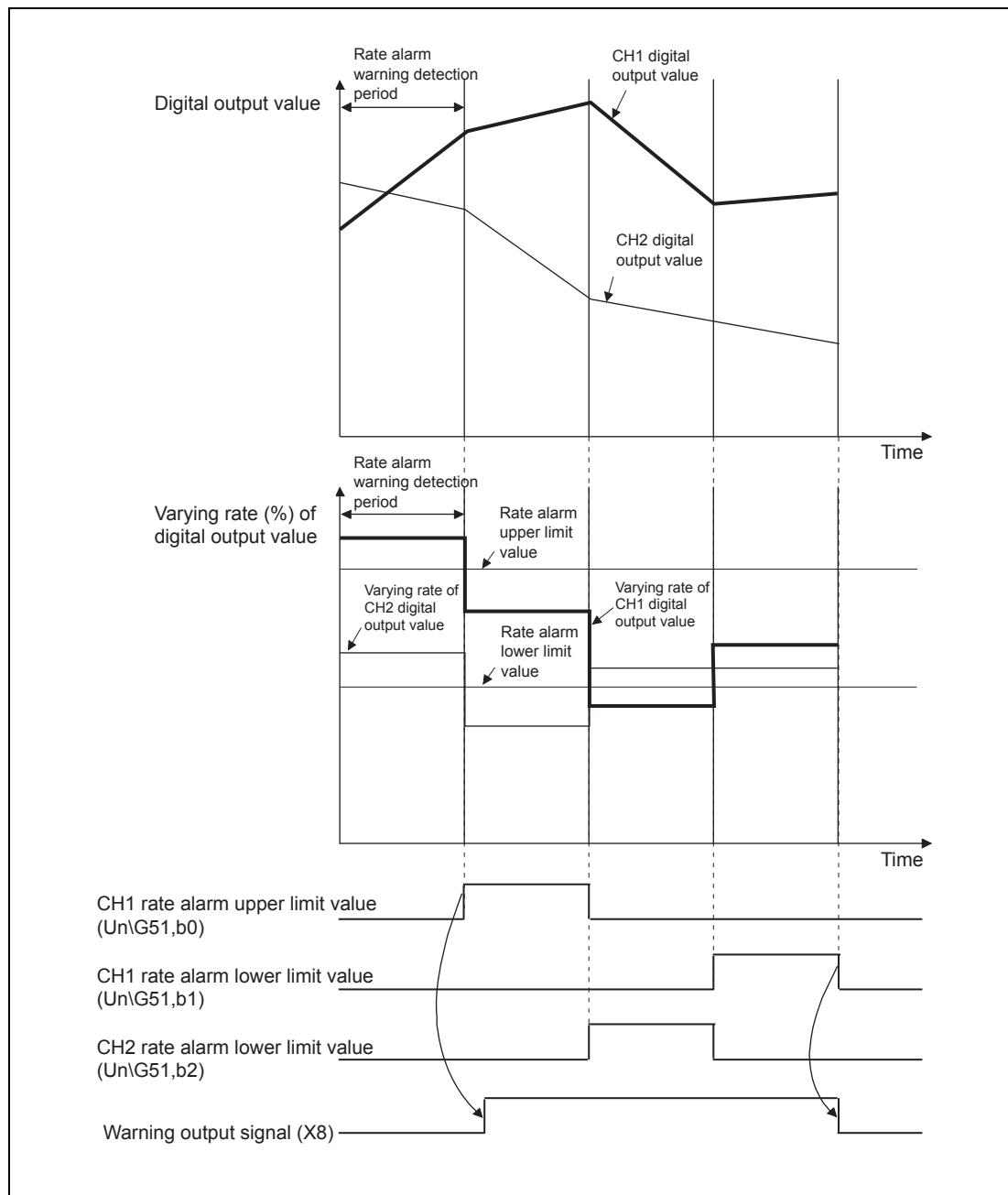

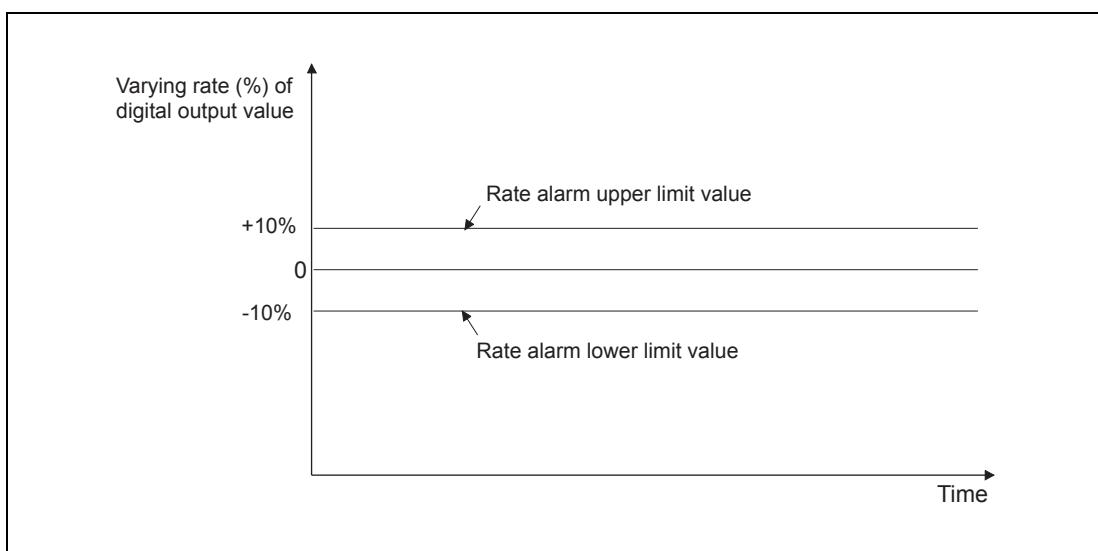

### Rate alarm

If the range of change in the digital output value sampled at intervals of the rate alarm warning detection period is equal to or greater than the rate alarm upper limit value or is equal to or less than the rate alarm lower limit value, the warning output flag (rate alarm) (Un\G51) and warning output signal (X8) turn ON and the ALM LED is lit to indicate the warning of the rate alarm.

If, after the output of the warning, the rate fell below the rate alarm upper limit value or rose above the rate alarm lower limit value and returned to within the setting range, "0" is stored into the bit position corresponding to the channel number of the warning output flag (rate alarm) (Un\G51). The warning output signal (X8) turns OFF only when all channels return to within the setting range

**Fig. 3-7: Warning output function (rate alarm)**

Set the rate alarm upper limit value/lower limit value in 0.1 %/s increments relative to the maximum value (32000) of the digital output value. The setting range is -32768 to 32767 (-3276.8 % to 3276.7 %).

The setting range of the rate alarm warning detection period is 80 to 5000 ms. When the period is set to 5000 ms, the digital values are compared at intervals of 5 seconds to detect the varying rate.

The rate alarm is judged by converting the rate alarm upper/lower limit value into the digit value per rate alarm warning detection period. The expression for the value used to make judgment per rate alarm warning detection period is as follows:

Value used to make judgment per rate alarm warning detection period [digit] =

rate alarm upper limit value or lower limit value  $\times 0.001 \times$  maximum value of the digital output value

$\times$  rate alarm warning detection period  $\div 1000$

● Example

The following is set for channel 1:

- Upper limit value of change rate: 30 % per second (300 is stored in buffer memory)

- Maximum digital output value: 32000

- Rate alarm warning detection period: 80 ms

The value [digit] used at every rate alarm warning detection period can be calculated as follows:

$$300 \times 0.001 \times 32000 \times 80 / 1000 = 768 \text{ (digit)}$$

Therefore, the current value is compared with the previous value every 80 ms in channel 1, and whether a difference of 768 (digit) or more is identified between them or not is determined.

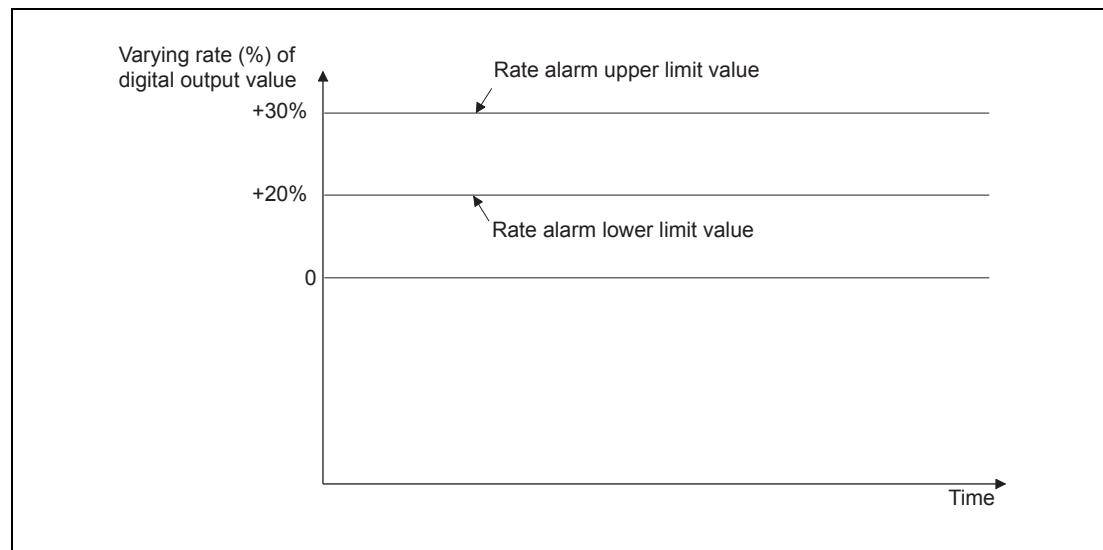

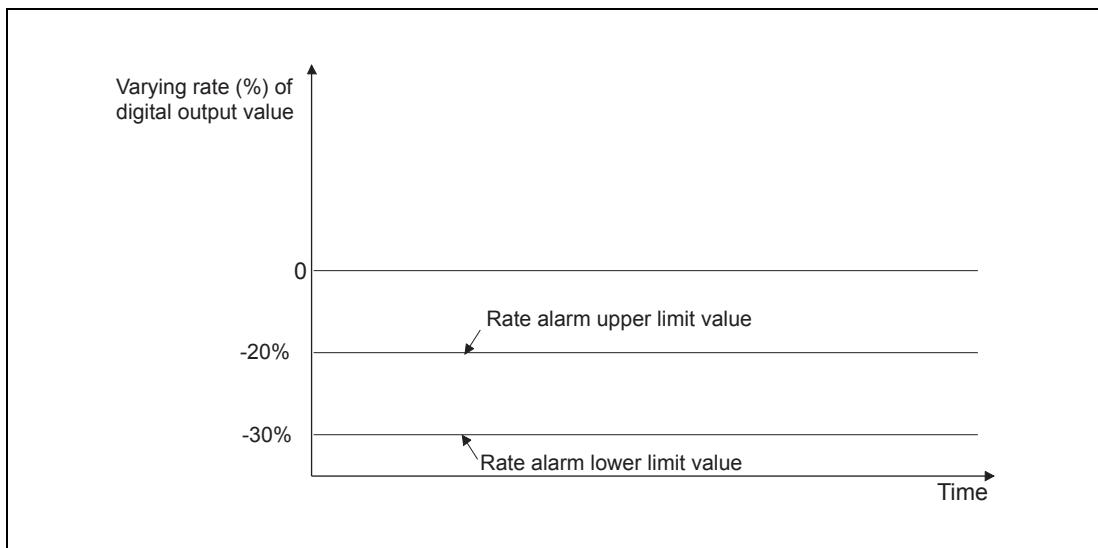

The rate alarm is useful to watch the varying rate of the digital output value in a limited range.

● Example of setting the rate alarm upper limit value/lower limit value when it is desired to watch that the digital output value increases within the specified range

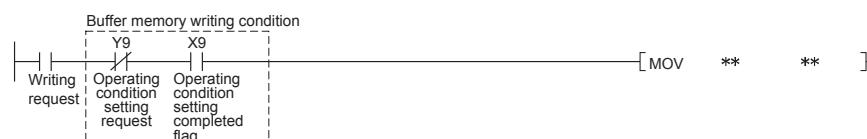

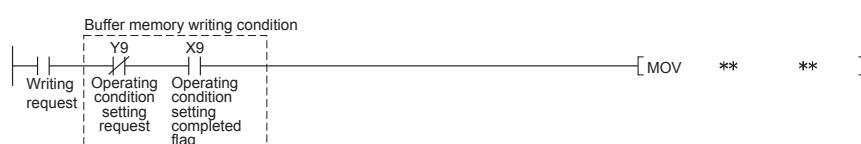

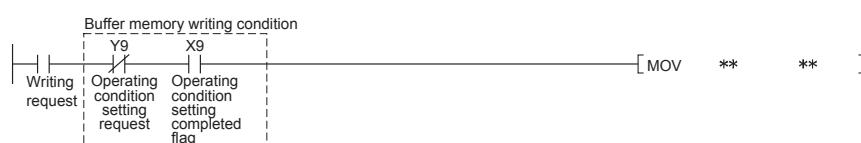

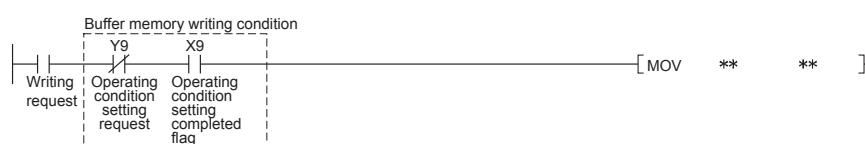

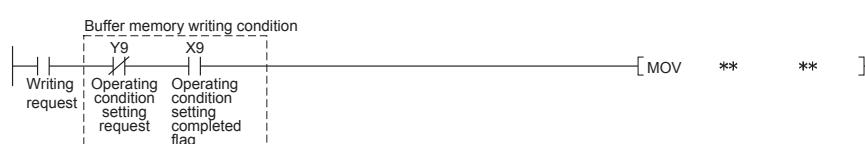

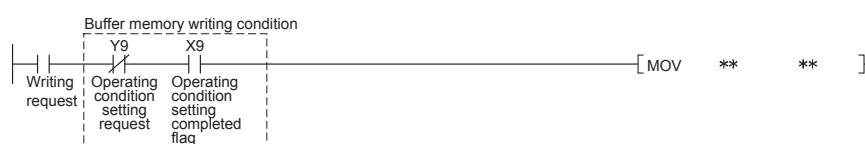

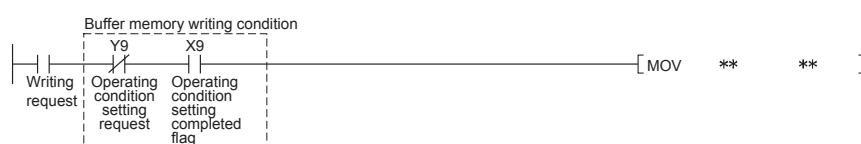

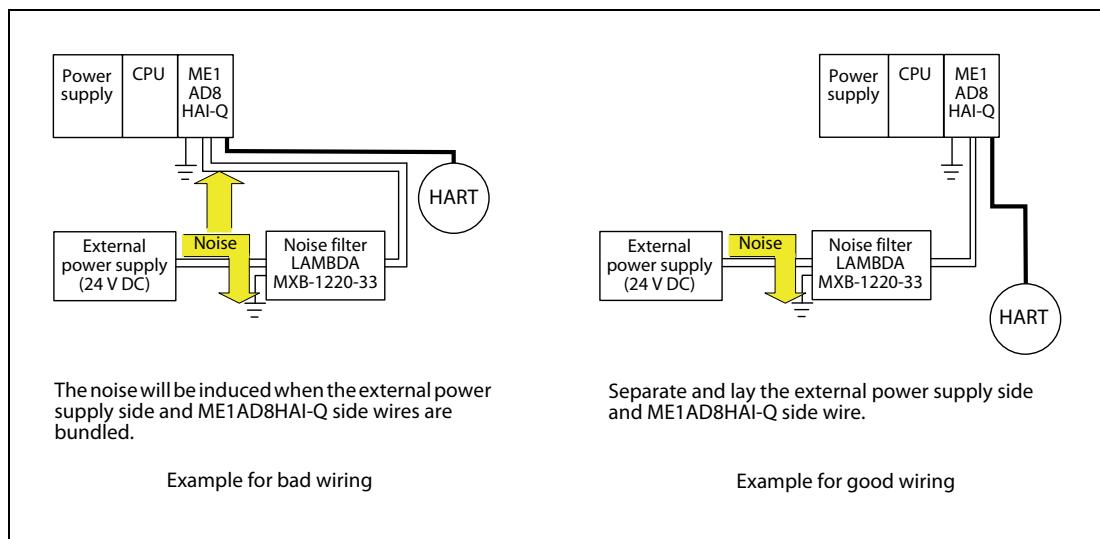

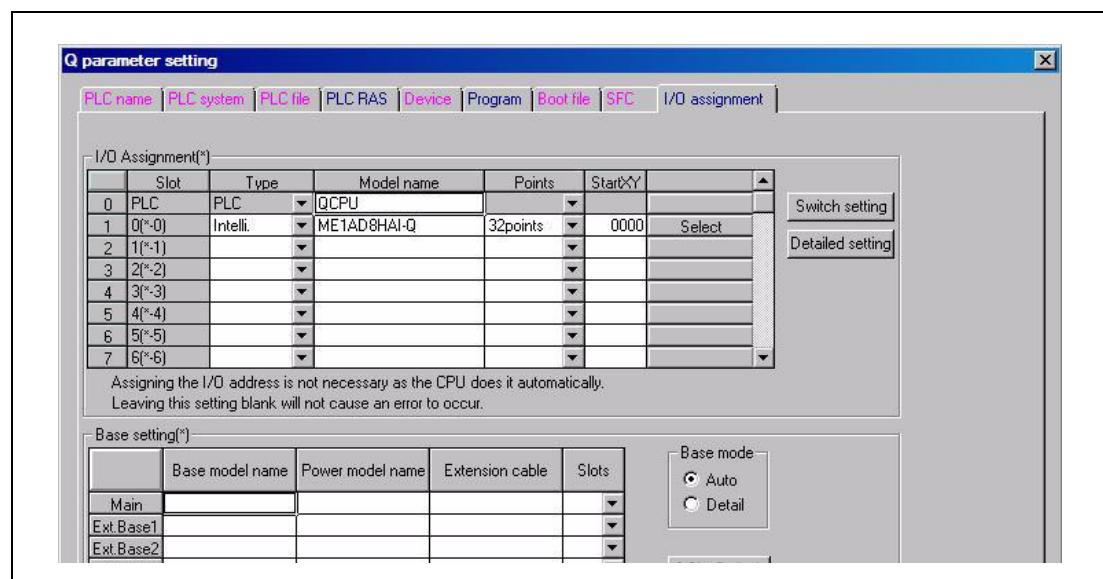

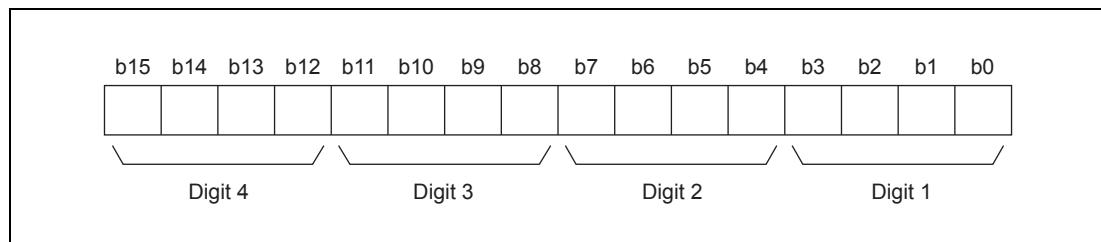

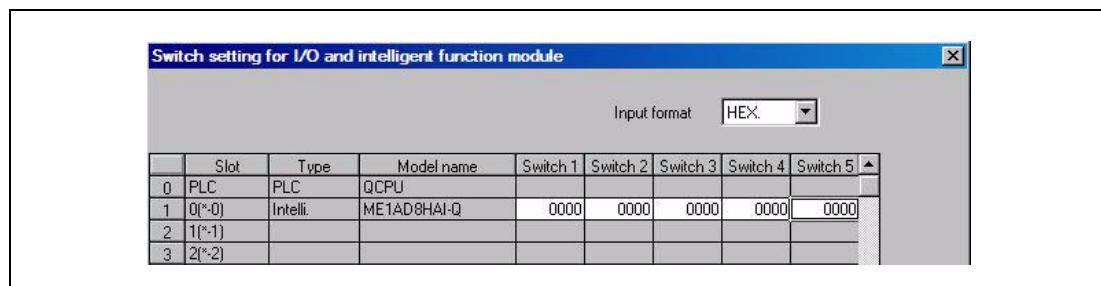

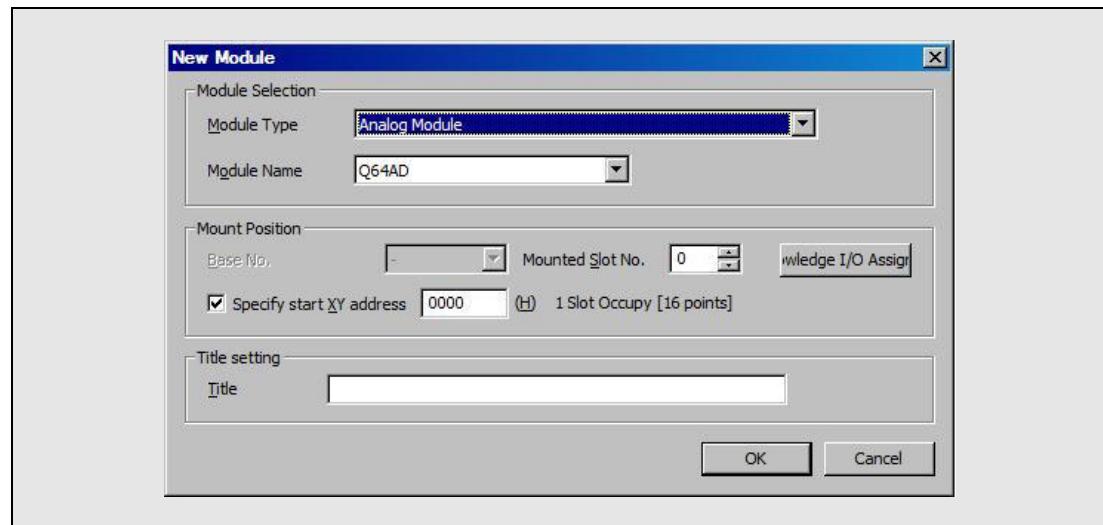

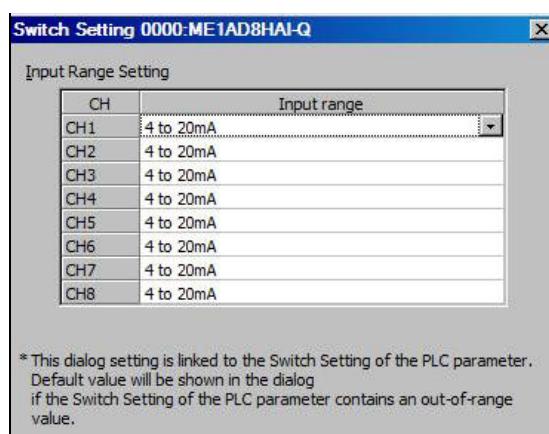

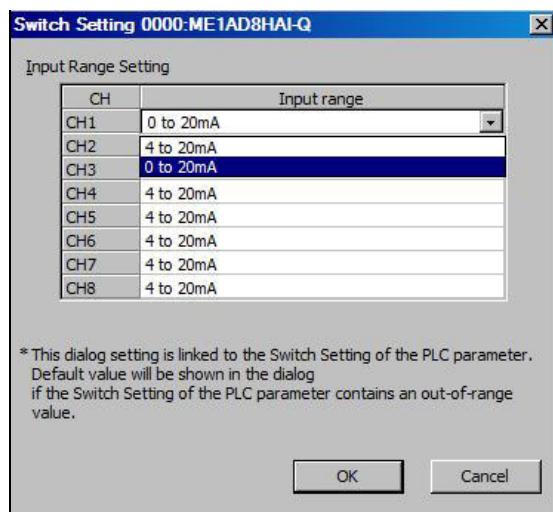

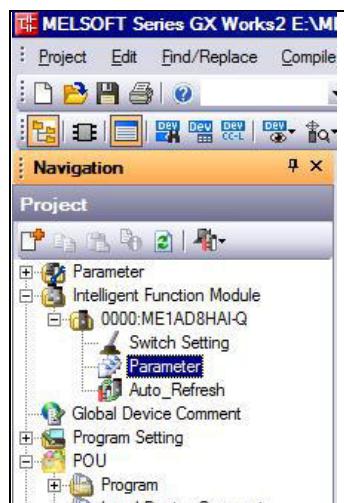

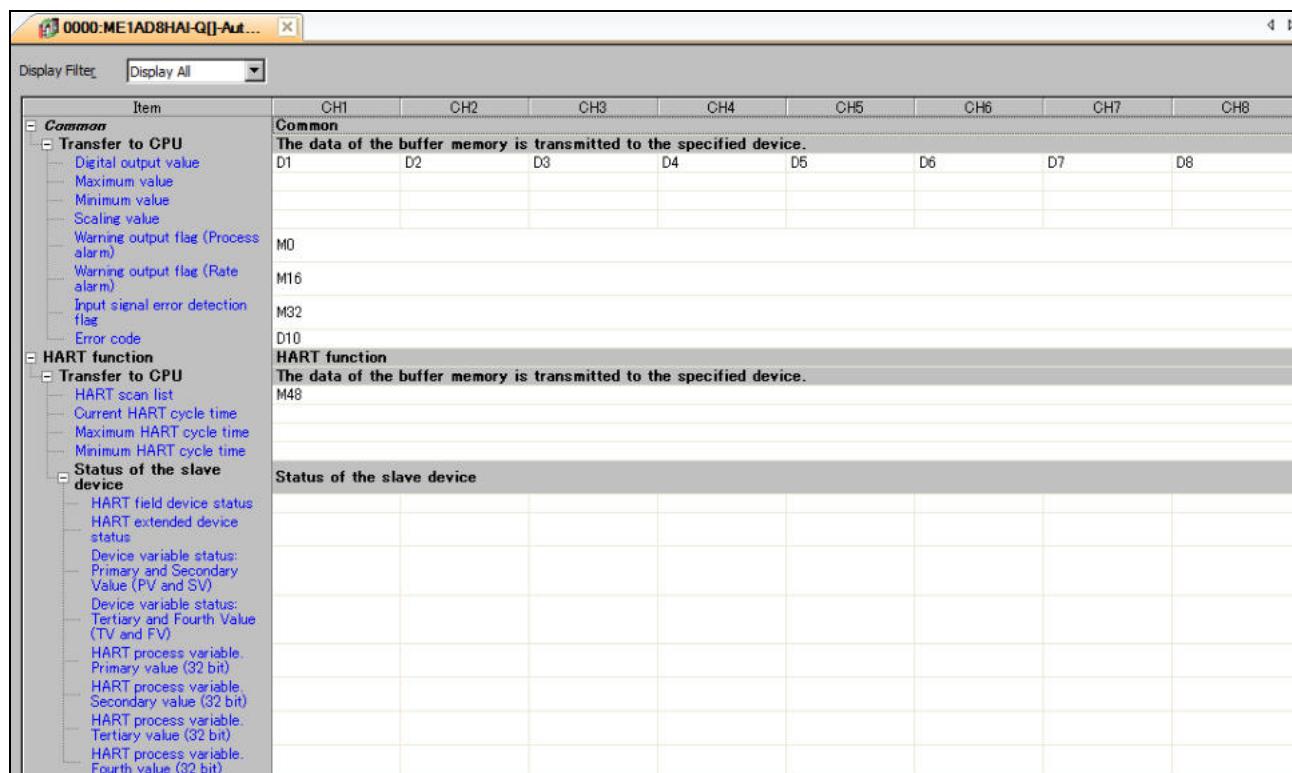

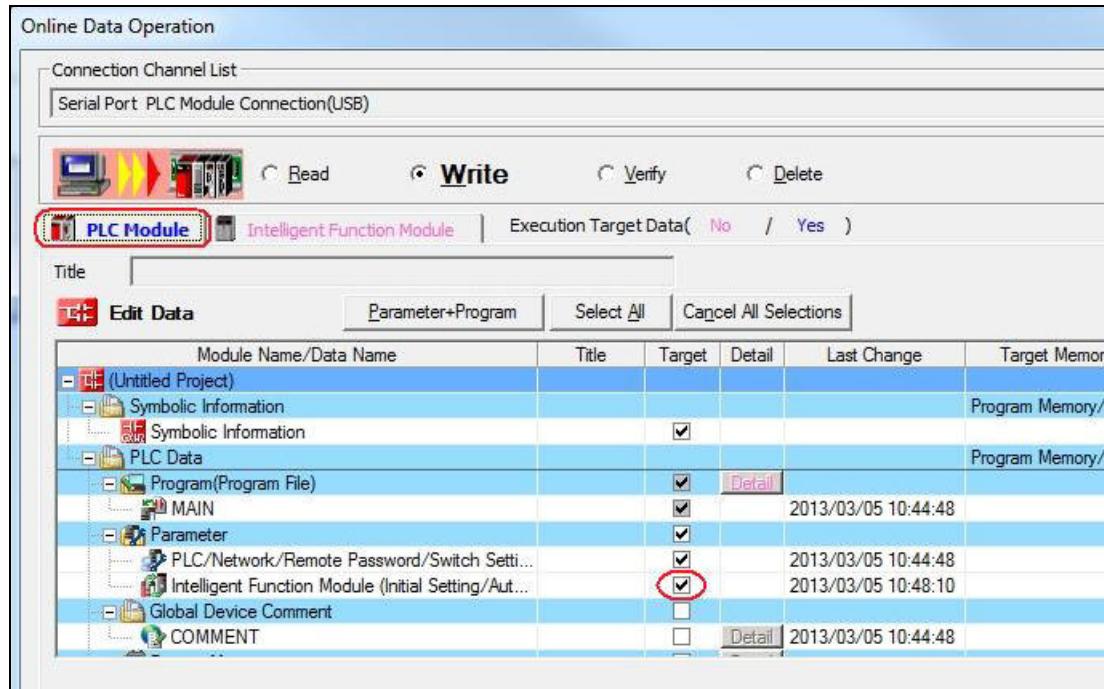

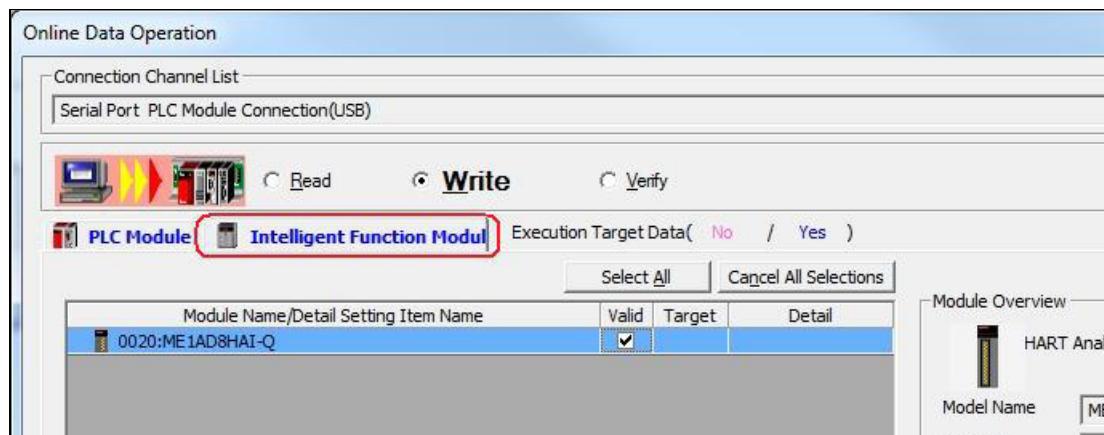

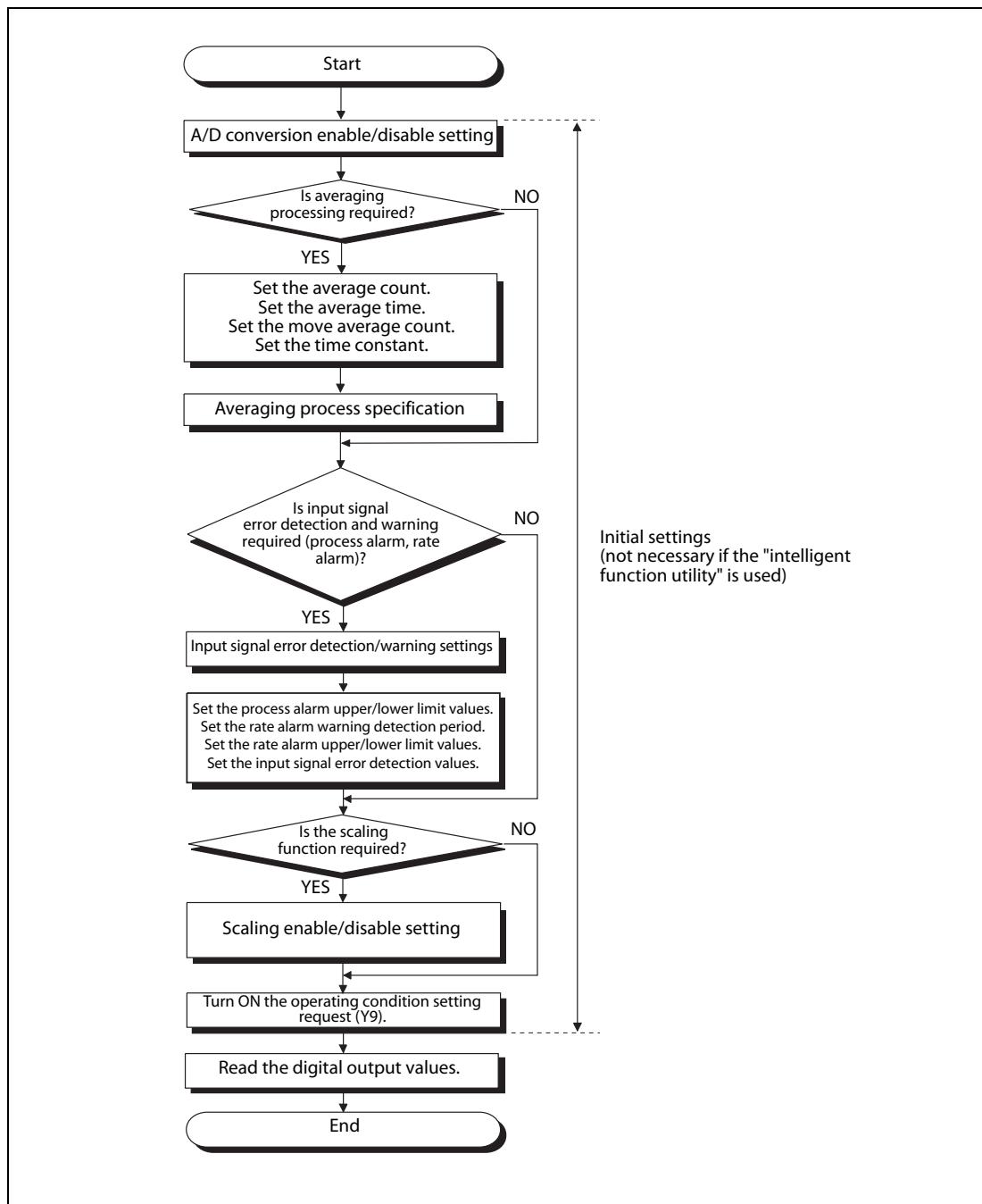

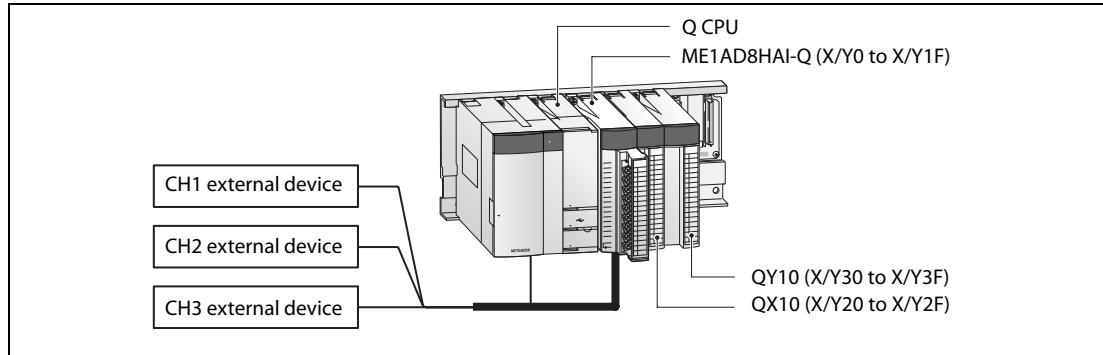

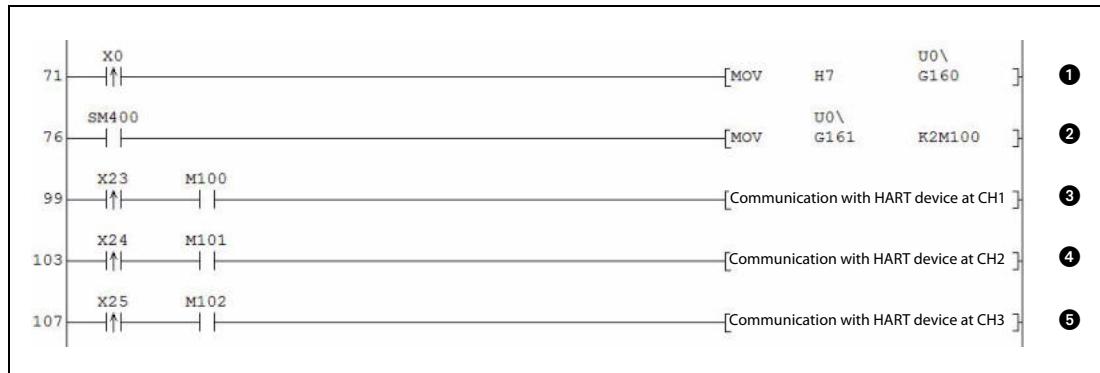

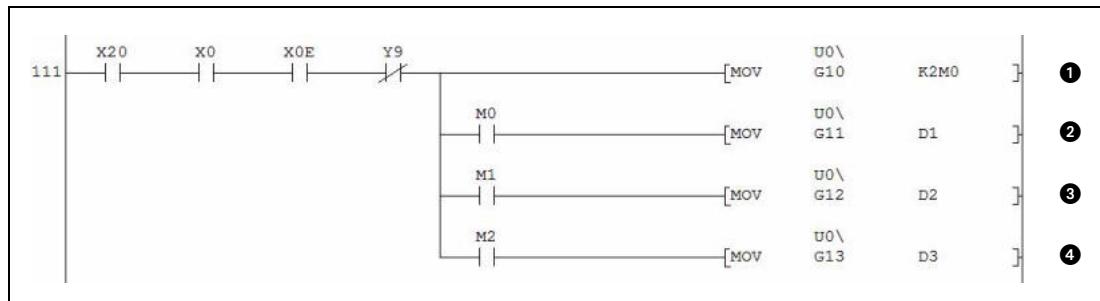

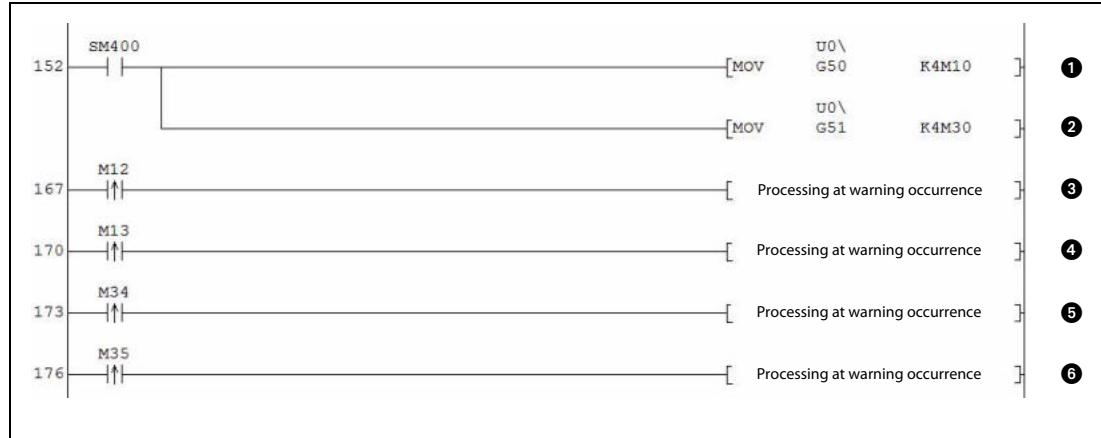

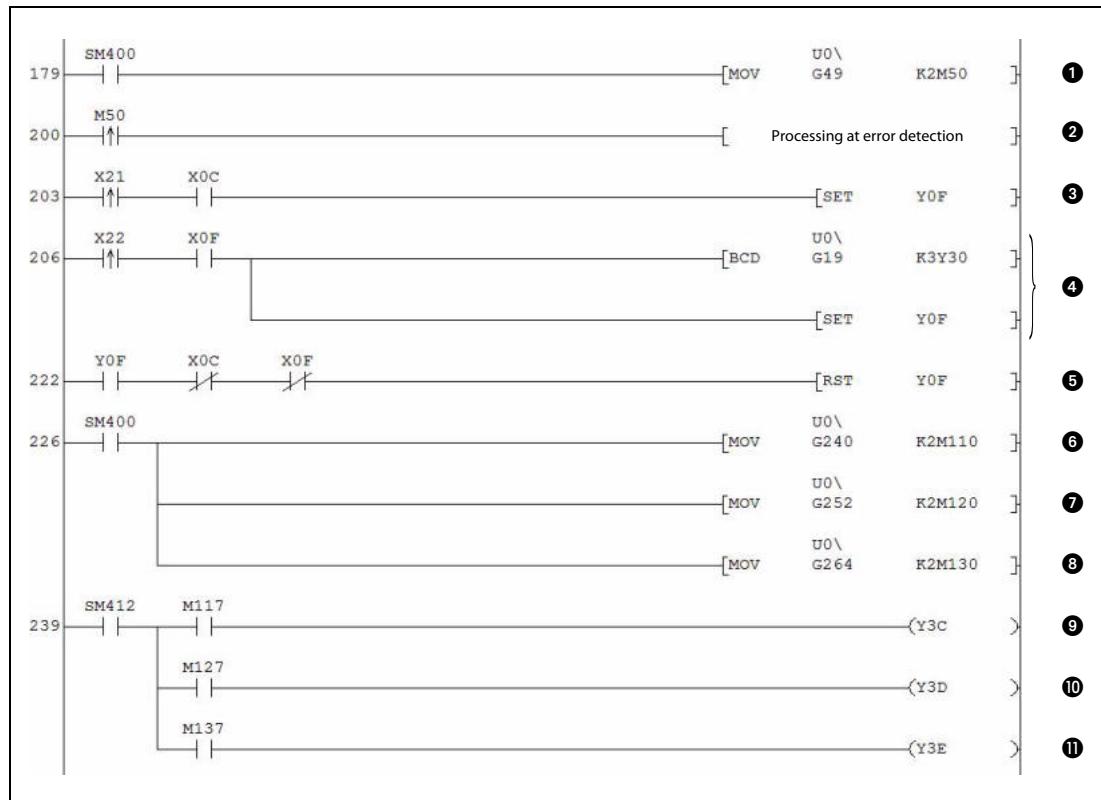

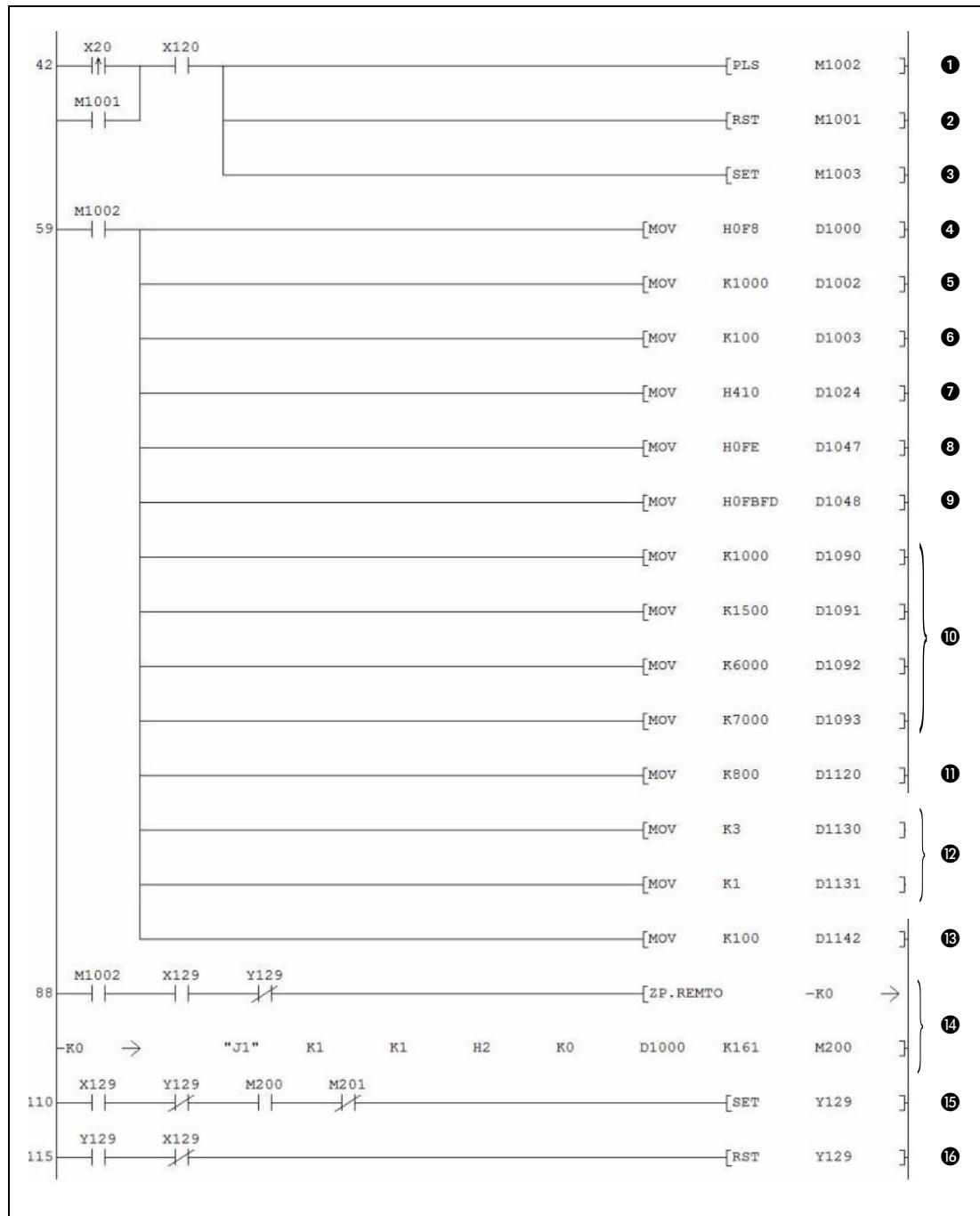

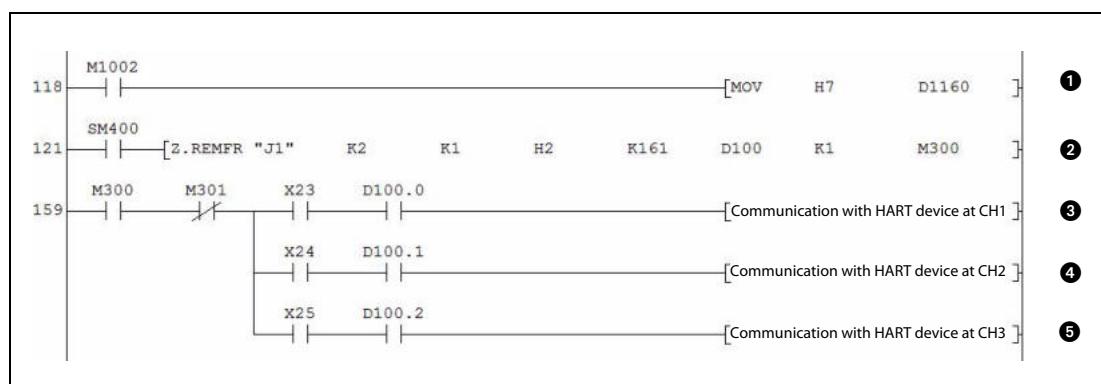

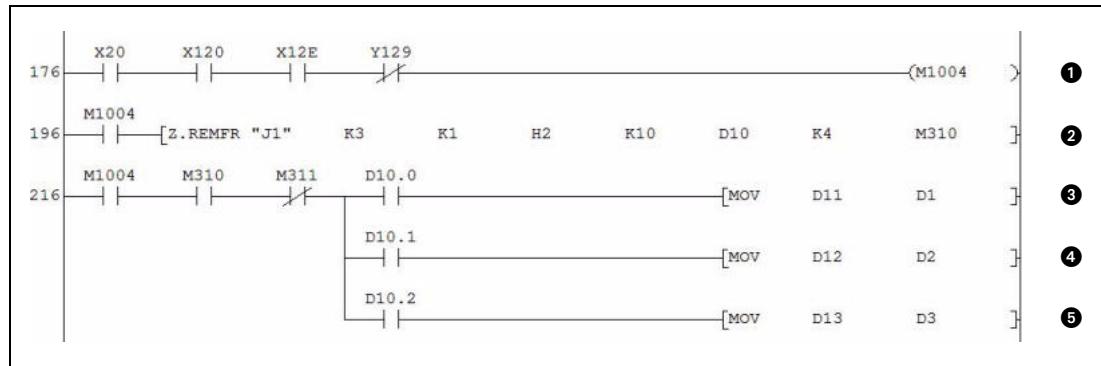

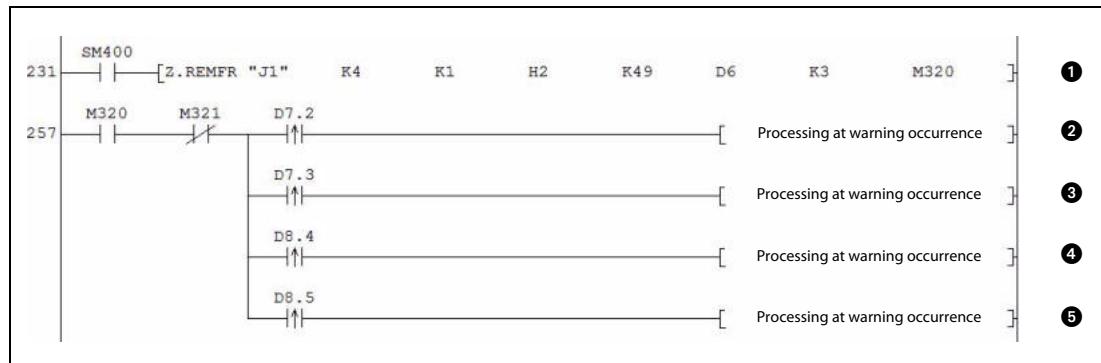

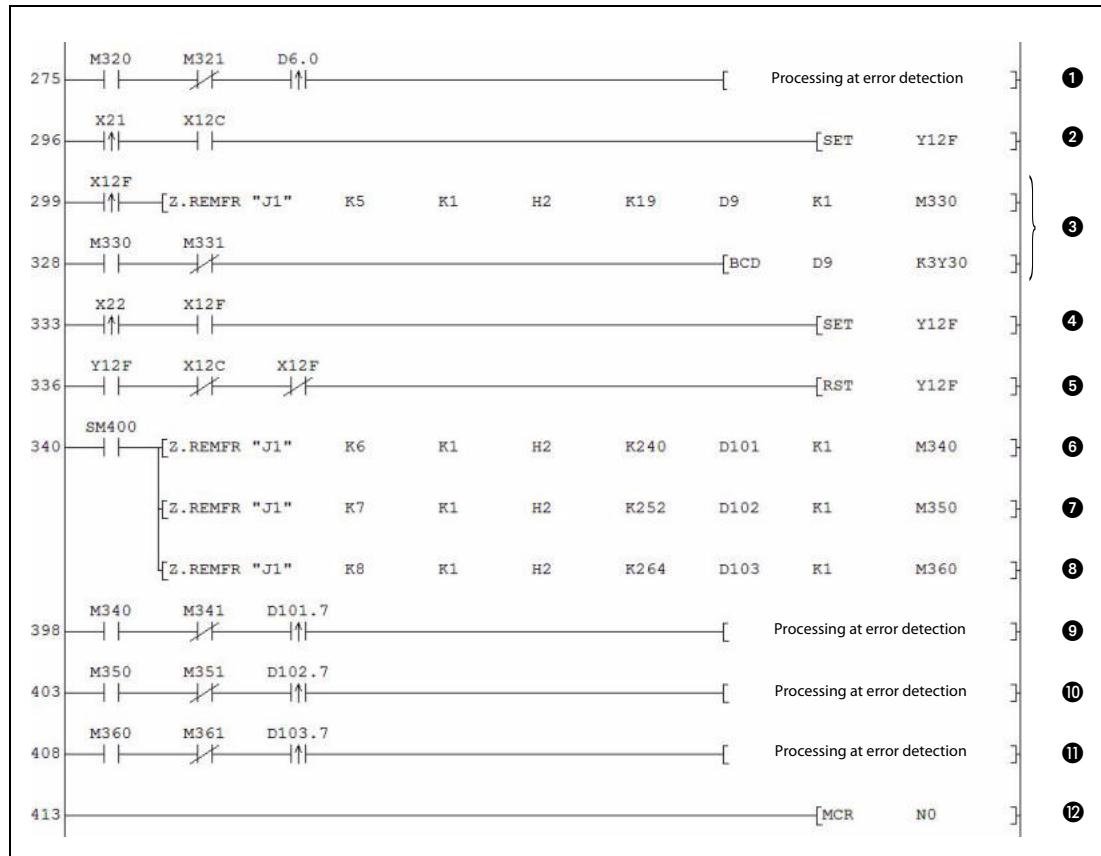

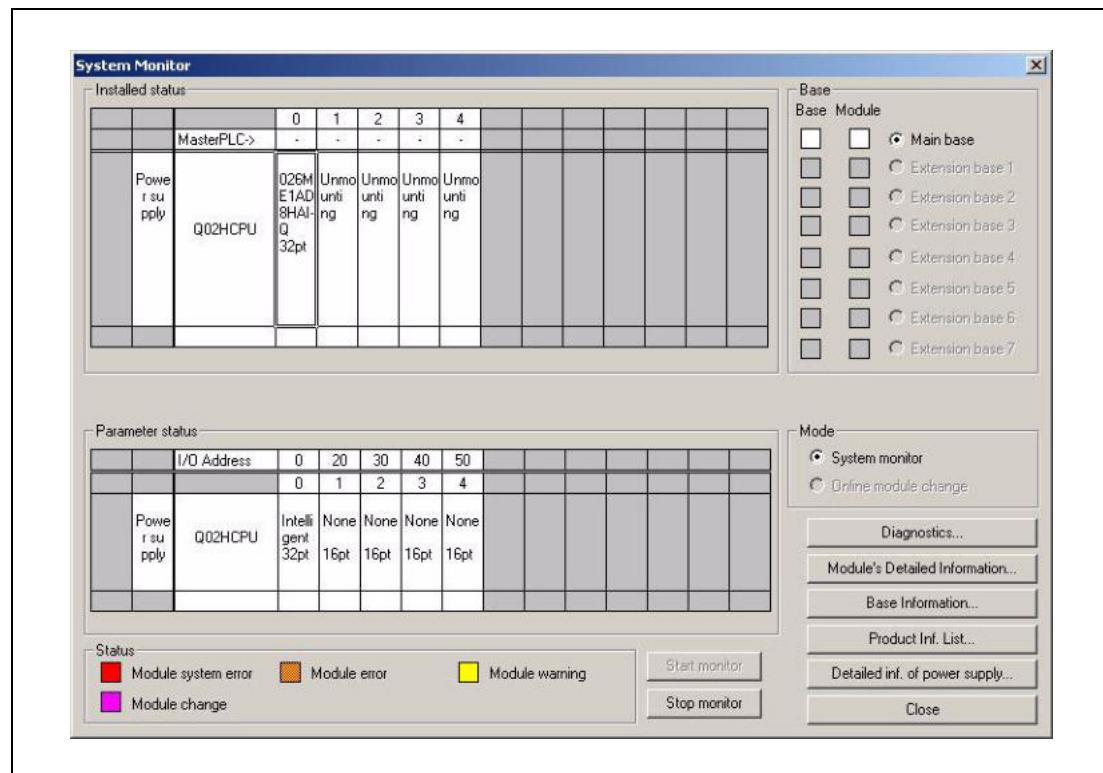

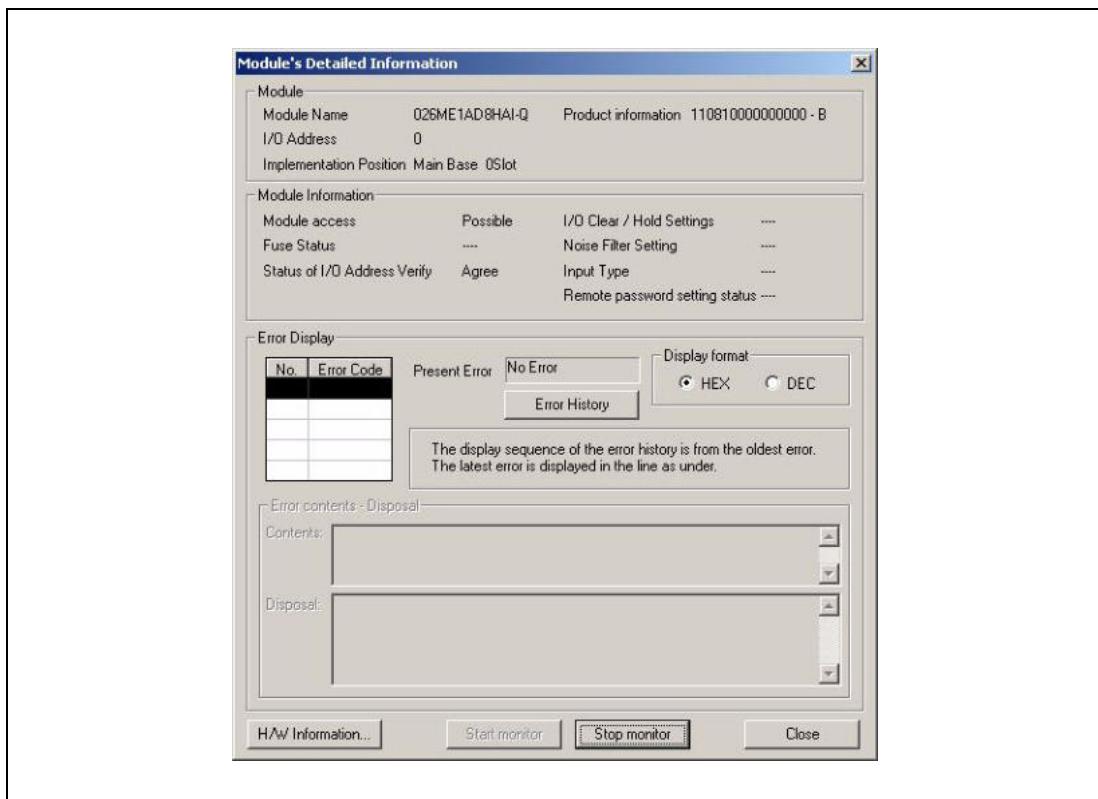

**Fig. 3-8: Rate alarm for increasing values**