<HVIC>

# M81774FP

#### 600V HIGH VOLTAGE HALF BRIDGE DRIVER

#### DESCRIPTION

M81774FP is high voltage Power MOSFET and IGBT gate driver for half bridge applications.

# **FEATURES**

- •Floating supply voltage up to 600V

- •Low quiescent power supply current

- •Separate sink and source current output up to ±1A (typ)

- Active Miller effect clamp NMOS with sink current up to 1A (typ)

- •Input noise filters (HIN,LIN,FO\_RST,FO)

- Over-current detection and output shutdown

- High side under voltage lockout

- •FO pin which can input and output Fault signals to communicate with controllers and synchronize the shut down with other phases

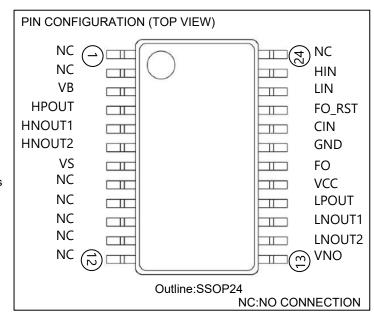

- •24-Lead SSOP PACKAGE

## **APPLICATIONS**

Power MOSFET and IGBT gate driver for Medium and Micro inverter or general purpose.

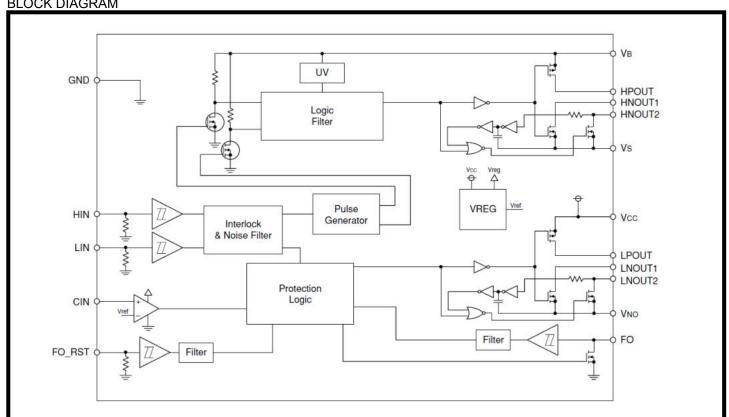

#### **BLOCK DIAGRAM**

# M81774FP

# 600V HIGH VOLTAGE HALF BRIDGE DRIVER

#### **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings indicate limitation beyond which destruction of device may occur. All voltage parameters are absolute voltage reference to GND unless otherwise specified.

| Symbol     | Parameter                                  | Test conditions          | Ratings                                     | Unit  |

|------------|--------------------------------------------|--------------------------|---------------------------------------------|-------|

| $V_{B}$    | High side floating supply absolute voltage |                          | -0.5 ~ 624                                  | V     |

| $V_{s}$    | High side floating supply offset voltage   |                          | $V_{B}$ -24 ~ $V_{B}$ +0.5                  | V     |

| $V_{BS}$   | High side floating supply voltage          | $V_{BS} = V_{B} - V_{S}$ | -0.5 ~ 24                                   | V     |

| $V_{HO^*}$ | High side output voltage                   |                          | $V_{S}$ -0.5 ~ $V_{B}$ +0.5                 | V     |

| $V_{CC}$   | Low side fixed supply voltage              |                          | -0.5 ~ 24                                   | V     |

| $V_{NO}$   | Power Ground                               |                          | V <sub>CC</sub> -24 ~ V <sub>CC</sub> +0.5  | V     |

| $V_{LO}$   | Low side output voltage                    |                          | V <sub>NO</sub> -0.5 ~ V <sub>CC</sub> +0.5 | V     |

| $V_{IN}$   | Logic input voltage                        | HIN, LIN, FO_RST         | -0.5 ~ V <sub>CC</sub> +0.5                 | V     |

| $V_{FO}$   | FO input/output voltage                    |                          | -0.5 ~ V <sub>CC</sub> +0.5                 | V     |

| $V_{CIN}$  | CIN input voltage                          |                          | -0.5 ~ V <sub>CC</sub> +0.5                 | V     |

| dVs/dt     | Allowable offset voltage slew rate         |                          | ±50                                         | V/ns  |

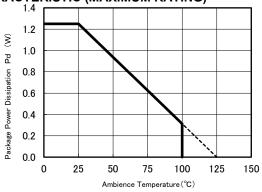

| Pd         | Package power dissipation                  | Ta = 25°C, On PCB        | 1.25                                        | W     |

| Κθ         | Linear derating factor                     | Ta > 25°C, On PCB        | 12.5                                        | mW/°C |

| Rth(j-c)   | Junction-case thermal resistance           |                          | 80                                          | °C/W  |

| Tj         | Junction temperature                       |                          | -40 ~ 125                                   | °C    |

| Topr       | Operation temperature                      |                          | -40 ~ 100                                   | °C    |

| Tstg       | Storage temperature                        | On PCB                   | -40 ~ 125                                   | °C    |

## **RECOMMENDED OPERATING CONDITIONS**

For proper operation the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to GND unless otherwise specified.

| 0 1 1           | Б.,                                        | T ( 199                  |                      | 1.1:4 |                    |      |  |

|-----------------|--------------------------------------------|--------------------------|----------------------|-------|--------------------|------|--|

| Symbol          | Parameter                                  | Test conditions          | Min.                 | Тур.  | Max.               | Unit |  |

| $V_{B}$         | High side floating supply absolute voltage |                          | V <sub>S</sub> +13.5 | Vs+15 | V <sub>s</sub> +20 | V    |  |

| $V_{s}$         | High side floating supply offset voltage   | V <sub>BS</sub> >13.5V   | -5                   | -     | 500                | V    |  |

| $V_{BS}$        | High side floating supply voltage          | $V_{BS} = V_{B} - V_{S}$ | 13.5                 | 15    | 20                 | V    |  |

| $V_{HO^*}$      | High side output voltage                   |                          | $V_s$                | -     | V <sub>s</sub> +20 | V    |  |

| $V_{CC}$        | Low side fixed supply voltage              |                          | 13.5                 | 15    | 20                 | V    |  |

| $V_{NO}$        | Power ground                               |                          | -0.5                 | -     | 5                  | V    |  |

| $V_{LO}$        | Low side output voltage                    |                          | $V_{NO}$             | -     | V <sub>cc</sub>    | V    |  |

| V <sub>IN</sub> | Logic input voltage                        | HIN,LIN,FO_RST           | 0                    | -     | V <sub>cc</sub>    | V    |  |

| $V_{FO}$        | FO input/output voltage                    |                          | 0                    | -     | V <sub>cc</sub>    | V    |  |

| $V_{CIN}$       | CIN input voltage                          |                          | 0                    | -     | 5                  | V    |  |

# THERMAL DERATING FACTOR CHARACTERISTIC (MAXIMUM RATING)

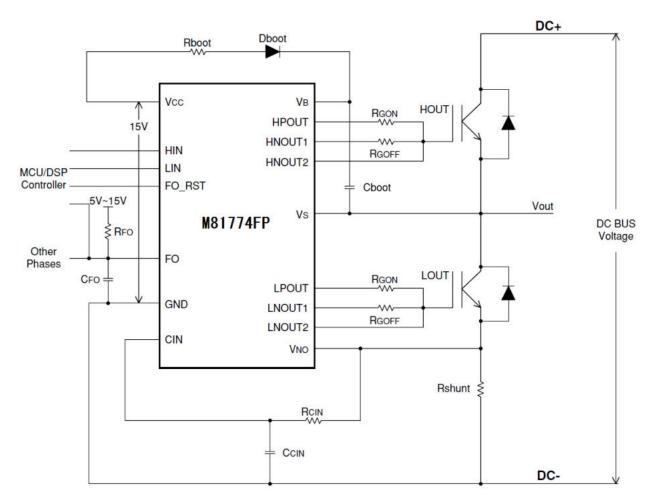

## **TYPICAL CONNECTION**

Note: If HVIC is working in high noise environment, it is recommended to connect a 1nF ceramic capacitor (CFO) to FO pin.

# M81774FP

## 600V HIGH VOLTAGE HALF BRIDGE DRIVER

ELECTRICAL CHARACTERISTICS (Ta=25°C, VCC=VBS (=VB-VS)=15V, unless otherwise specified) Symbol Parameter Test conditions Unit Min. Тур. Max. 1.0 High side leakage current V<sub>R</sub>=V<sub>S</sub>=600V μΑ HIN=LIN=0V 0.15 0.5 VBS quiescent supply current mΑ VCC quiescent supply current HIN=LIN=0V 0.7 1.5 mΑ High level output voltage I<sub>0</sub>=0A, HPOUT, LPOUT 14.5 15 V I<sub>O</sub>=0A, HNOUT1, LNOUT1 0 0.5 ٧ Low level output voltage V. High level input threshold voltage HIN, LIN, FO\_RST 4.0 \_ V Low level input threshold voltage HIN, LIN, FO\_RST 0.6 V High level input bias current VIN=5V 0.6 1.0 1.4 mΑ Low level input bias current VIN=0V -0.01 0 mΑ tFilter Input signals filter time HIN, LIN, FO RST, FO 100 200 500 ns High side active Miller clamp NMOS VIN=0V  $V_{_{\rm HNO2}}$ 2.0 3.4 4.0 input threshold voltage Low side active Miller clamp NMOS  $V_{LNO2}$ VIN=0V 5.5 7.6 8.5 V input threshold voltage VIN=0V tV. Active Miller clamp NMOS filter time 400 ns IFO=1mA ٧ Low level FO output voltage 0.95 ٧ High level FO input threshold voltage 4.0 ٧ Low level FO input threshold voltage 0.6 VBS supply UV reset voltage 10.5 11.3 12.1  $V_{RS}$ VBS supply UV trip voltage 10 10.8 11.6 ٧ 0.2 0.5 8.0 V VBS supply UV hysteresis voltage  $V_{RSIN/h} = V_{RSIN/r} - V_{RSIN/r}$ 4 tV, VBS supply UV filter time 16 us ٧<sub></sub> CIN trip voltage 0.4 0.5 0.6 ٧ POR trip voltage 4.5 6.5 8.5 Output high level short circuit pulsed HPOUT(LPOUT)=0V,HIN=5V,PW≦5us 1 Α  $I_{OH}$ current Output low level short circuit pulsed current HNOUT1(LNOUT1)=15V,LIN=5V,PW≦5us -1 Α Active Miller clamp NMOS output HNOUT2(LNOUT2)=15V,LIN=5V,PW≦5us -1 l<sub>OL2</sub> low level short circuit pulsed current R 0 Output high level on resistance  $I_0 = -1A, R_{OH} = (V_{OH} - V_O)/|I_O|$ 15 R Output low level on resistance  $I_0 = 1A, R_{011} = V_0/I_0$ 15 Ω Active Miller clamp NMOS output  $\mathsf{R}_{_{\mathsf{OL2}}}$  $I_0 = 1A, R_{012} = V_0/I_0$ 15 0 low level on resistance tdLH(HO) High side turn-on propagation delay HPOUT short to HNOUT1and2. CL=1nF 0.4 0.8 1.25 us tdHL(HO) High side turn-off propagation delay HPOUT short to HNOUT1and2, CL=1nF 0.35 0.74 1.2 us tdLH(LO) HPOUT short to HNOUT1and2, CL=1nF 0.4 8.0 1.25 Low side turn-on propagation delay us 0.35 0.74 1.2 tdHL(LO) Low side turn-off propagation delay HPOUT short to HNOUT1and2, CL=1nF us tr Output turn-on rise time CL=1nF 40 ns Output turn-off fall time CL=1nF 40 ns Delay matching, high side turn-on  $\Delta tdLH$ tdLH(HO)-tdHL(LO) 60 ns and low side turn-off Delay matching, high side turn-off  $\Delta tdHL$ tdLH(LO)-tdHL(LO) 60 ns and low side turn-on

Note: Typ is not specified

**FUNCTION TABLE (Q: Keep previous status)**

|     |     | _ ( =4: ::== ; | - P |               | -,         |             |      |      |                |                                          |

|-----|-----|----------------|-----|---------------|------------|-------------|------|------|----------------|------------------------------------------|

| HIN | LIN | FO_<br>RST     | CIN | FO<br>(Input) | VBS<br>/UV | VCC<br>/POR | HOUT | LOUT | FO<br>(Output) | Behavioral state                         |

| H→L | L   | L              | L   | _             | Н          | Н           | L    | L    | Н              |                                          |

| H→L | Н   | L              | L   | _             | Н          | Н           | L    | Н    | Н              |                                          |

| L→H | L   | L              | L   | _             | Н          | Н           | Н    | L    | Н              |                                          |

| L→H | Н   | L              | L   | _             | Н          | Н           | Q    | Q    | Н              | Interlock active                         |

| Х   | Н   | Х              | Н   | _             | Х          | Н           | L    | L    | L              | CIN tripping when LIN = H                |

| Χ   | L   | Х              | Н   | _             | X          | Н           | Q    | Q    | Н              | CIN not tripping when LIN = L            |

| Χ   | X   | Х              | Χ   | L             | X          | Н           | L    | L    | L              | Output shuts down when FO = L            |

| Χ   | X   | Х              | Χ   | _             | X          | L           | L    | L    | Н              | VCC power reset                          |

| Х   | L   | L              | L   | _             | L          | Н           | L    | L    | Н              | VBS power reset                          |

| Х   | Н   | L              | L   | _             | L          | Н           | L    | Н    | Н              | VBS power reset is tripping when LIN = H |

Note1: "L" status of VBS/UV indicates a high side UV condition; "L" status of VCC/POR indicates a VCC power reset condition.

Note2: In the case of both input signals (HIN and LIN) are "H", output signals (HOUT and LOUT) keep previous status.

Note3 : X (HIN) :  $L\rightarrow H$  or  $H\rightarrow L$ . Other : H or L.

Note4: Output signal (HOUT) is triggered by the edge of input signal.

# **FUNCTIONAL DESCRIPTION**

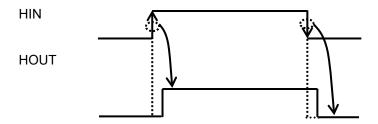

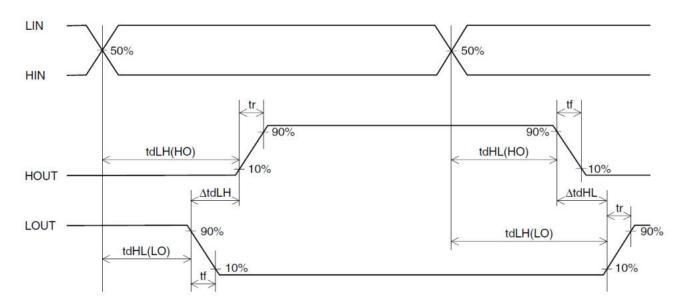

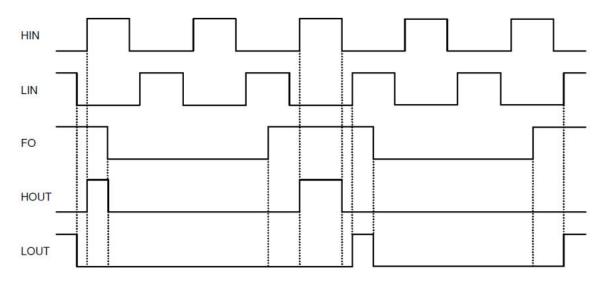

# 1. INPUT/OUTPUT TIMING DIAGRAM

#### 2. INPUT/OUTPUT TIMING DIAGRAM

When the input signals (HIN/LIN) are high level at the same time, the outputs (HOUT/LOUT) keep their previous status. But if signals (HIN/LIN) are going to high level simultaneously, HIN signals will get active and cause HOUT to enter "H" status.

Note1: The minimum input pulse width at HIN/LIN should be to more than 500ns (because of HIN/LIN input noise filter circuit).

Note2 : If a high-high status of input signals (HIN/LIN) is ended with only one input signal entering low level and another still being in high level, the output will enter high-low status after the delay match time (not shown in the figure above).

Note3: Delay times between input and output signals are not shown in the figure above.

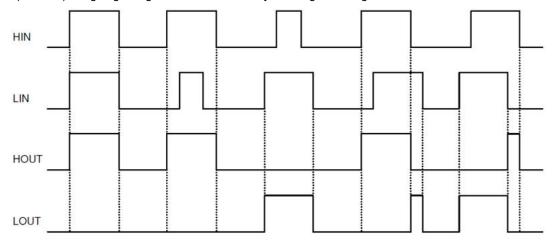

## 3. SHORT CIRCUIT PROTECTION TIMING DIAGRAM

When an over-current is detected by exceeding the threshold at the CIN and LIN is at high level at the same time, the short circuit protection will get active and shutdown the outputs while FO will issue a low level (indicating a fault signal).

The fault output latch is reset by a high level signal at FO\_RST pin and then FO will return to high level while the output of the driver will respond to the following active input signal.

Note1: Delay times between input and output signals are not shown in the figure above.

Note2: The minimum FO\_RST pulse width should be more than 500ns (because of FO\_RST input filter circuit).

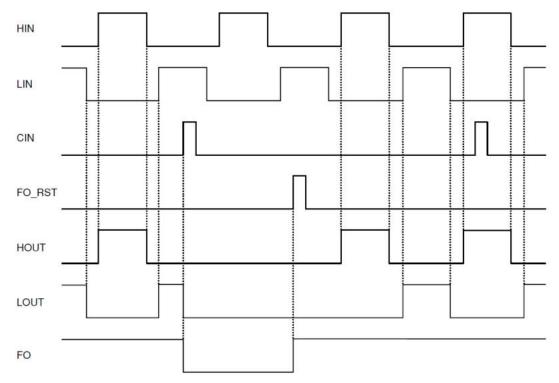

#### 4. FO INPUT TIMING DIAGRAM

When FO is pulled down to low level in case the FO of other phases becomes low level (fault happened) or the MCU/DSP sets FO to low level, the outputs (HOUT, LOUT) of the driver will be shut down. As soon as FO goes high again, the output will respond to the following active input signal.

Note1: Delay times between input and output signals are not shown in the figure above.

Note2: The minimum FO pulse width should be more than 500ns (because of FO input filter circuit).

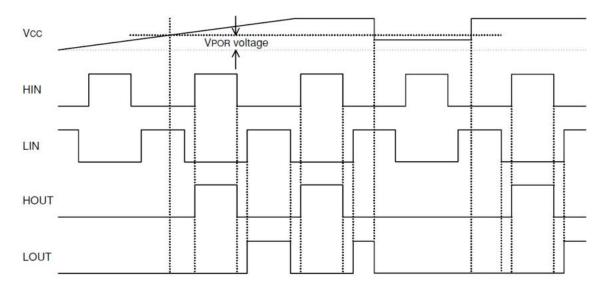

## 5. LOW SIDE VCC SUPPLY POWER RESET SEQUENCE

When the VCC supply voltage is lower than power reset trip voltage, the power reset gets active and the outputs (HOUT/LOUT) become "L". As soon as the VCC supply voltage goes higher than the power reset trip voltage, the outputs will respond to the following active input signals.

Note1: Delay times between input and output signals are not shown in the figure above

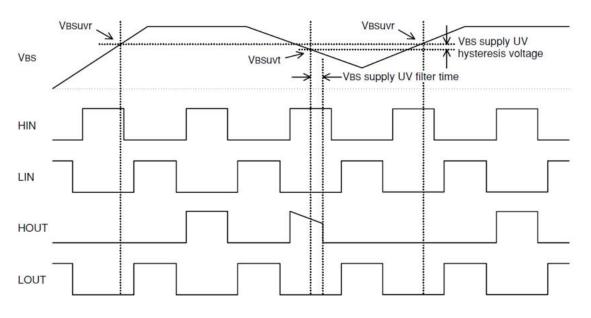

## 6. HIGH SIDE VBS SUPPLY UNDER VOLTAGE LOCKOUT SEQUENCE

When VBS supply voltage drops below the VBS supply UV trip voltage and the duration in this status exceeds the VBS supply UV filter time, the output of the high side is locked. As soon as the VBS supply voltage rises above the VBS supply UV reset voltage, the output will respond to the following active HIN signal.

Note1: Delay times between input and output signals are not shown in the figure above.

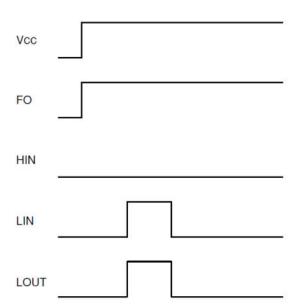

#### 7. POWER START-UP SEQUENCE

At power supply start-up the following sequence is recommended when bootstrap supply topology is used.

- ① Apply VCC.

- 2 Make sure that FO is at high level.

- ③ Set LIN to high level and HIN to low level so that bootstrap capacitor could be charged.

- 4 Set LIN to low level.

Note: If two power supply are used for supplying VCC and VBS individually, it is recommended to set VCC first and then set VBS.

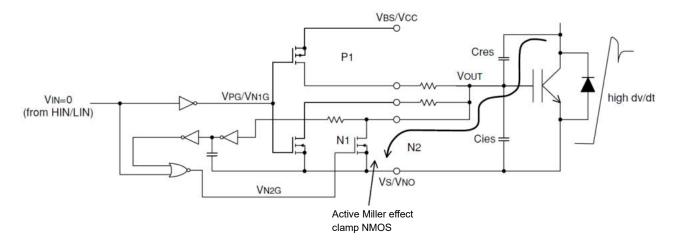

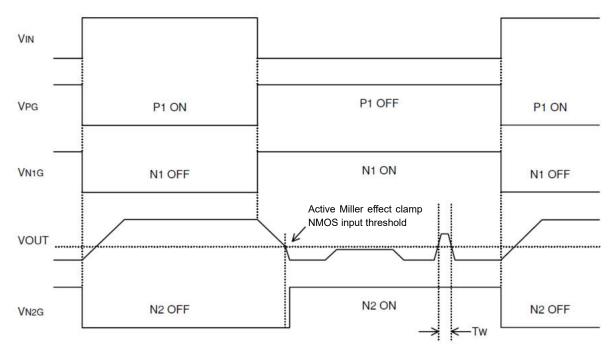

#### 8. ACTIVE MILLER EFFECT CLAMP NMOS OUTPUT TIMING DIAGRAM

The structure of the output driver stage is shown in following figure. This circuit structure employs a solution for the problem of the Miller current through Cres in IGBT switching applications. Instead of driving the IGBT gate to a negative voltage to increase the safety margin, this circuit structure uses a NMOS to establish a low impedance path to prevent the self-turn-on due to the parasitic Miller capacitor in power switches.

When HIN/LIN is at low level and the voltage of the VOUT (IGBT gate voltage) is below active Miller effect clamp NMOS input threshold voltage, the active Miller effect clamp NMOS is being turned on and opens a low resistive path for the Miller current through Cres.

Active Miller effect clamp NMOS keeps turn-on if Tw does not exceed active Miller clamp NMOS filter time

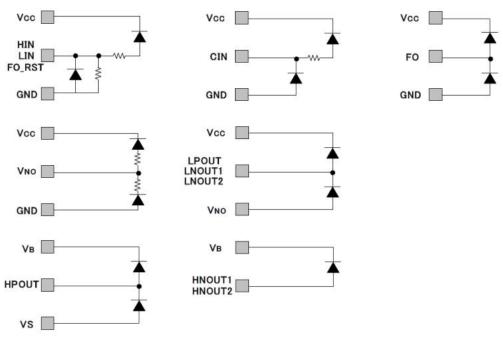

## INTERNAL DIODE CLAMP CIRCUITS FOR INPUT AND OUTPUT

# **ENVIRONMENTAL CONSCIOUSNESS**

M81774FP is compliant with the Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment (RoHS) directive 2011/65/EU+(EU)2015/863.

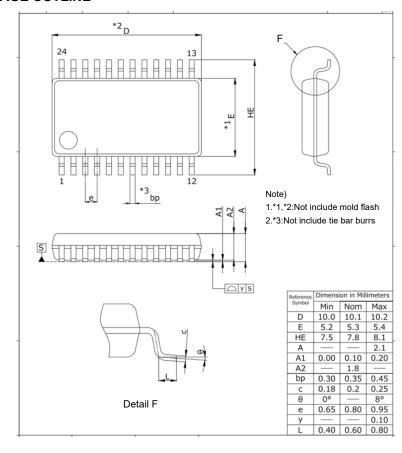

# **PACKAGE OUTLINE**

Recommended Mount Pad

| SYMBOLS   | DIMENSIONS IN MILLIMETERS |      |     |  |  |  |  |

|-----------|---------------------------|------|-----|--|--|--|--|

| STIVIDOLS | MIN                       | NOM  | MAX |  |  |  |  |

| e1        | _                         | 7.62 | -   |  |  |  |  |

| 12        | 1.27                      | _    | _   |  |  |  |  |

| е         | _                         | 0.8  | _   |  |  |  |  |

| b2        | _                         | 0.5  | _   |  |  |  |  |

The above is one example.

Please design the mount pad with your evaluation.

# **Main Revision for this Edition**

|              | Revision      |                                                                                                                                                                                                                                                        |  |  |

|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date         | Pages         | Points                                                                                                                                                                                                                                                 |  |  |

| 15 Jun. 2017 | -             | New                                                                                                                                                                                                                                                    |  |  |

| 8 May. 2018  | -<br>P2<br>P4 | "PRELIMINARY" was deleted "( )" was deleted in Ratings of Pd, K $\theta$ ,Rth(j-c) Test conditions of V $_{OH}$ was changed to "I $_{O}$ =0A" from "I $_{O}$ =-20mA" Test conditions of V $_{OL}$ was changed to "I $_{O}$ =0A" from "I $_{O}$ = 20mA" |  |  |

| 28 Apr. 2021 | -             | Update format                                                                                                                                                                                                                                          |  |  |

|              |               |                                                                                                                                                                                                                                                        |  |  |

|              | 8 May. 2018   | 15 Jun. 2017 -  8 May. 2018 -  P2  P4                                                                                                                                                                                                                  |  |  |

# **Important Notice**

The information contained in this datasheet shall in no event be regarded as a guarantee of conditions or characteristics. This product has to be used within its specified maximum ratings, and is subject to customer's compliance with any applicable legal requirement, norms and standards.

Except as otherwise explicitly approved by Mitsubishi Electric Corporation in a written document signed by authorized representatives of Mitsubishi Electric Corporation, our products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

In usage of power semiconductor, there is always the possibility that trouble may occur with them by the reliability lifetime such as Thermal Cycle or others, or when having assembling stress (e.g. high temperature of reflow process, or rinse after the reflow), or when used under special operating conditions (e.g. rise/fall time of the power supply voltage, or excessive voltage/current injection), or when used under special circumstances (e.g. condensation, high humidity, dusty, salty, highlands, environment with lots of organic matter / corrosive gas / explosive gas, or situations which terminals of semiconductor products receive strong mechanical stress). Therefore, please pay sufficient attention to such circumstances. Further, depending on the technical requirements, our semiconductor products may contain environmental regulation substances, etc. If there is necessity of detailed confirmation, please contact our nearest sales branch or distributor.

The contents or data contained in this datasheet are exclusively intended for technically trained staff. Customer's technical departments should take responsibility to evaluate the suitability of Mitsubishi Electric Corporation product for the intended application and the completeness of the product data with respect to such application. In the customer's research and development, please evaluate it not only with a single semiconductor product but also in the entire system, and judge whether it's applicable. As required, pay close attention to the safety design by installing appropriate fuse or circuit breaker between a high voltage/large current power supply and power semiconductor products(e.g. IGBT, MOSFET) to prevent secondary damage. Please also pay attention to the application note and the related technical information.

Publication Date : Apr. 2021

# Keep safety first in your circuit designs!

Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

# Notes regarding these materials

- •These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- •Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- •All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Mitsubishi Electric Corporation by various means, including the Mitsubishi Semiconductor home page (http://www.MitsubishiElectric.com/).

- •When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- •Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- •The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- •If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or re-export contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- •Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.