# WINSTAR Display

# **OLED SPECIFICATION**

Model No:

WEA002002A

## **General Specification**

| Item                 | Dimension               | Unit              |  |  |  |  |

|----------------------|-------------------------|-------------------|--|--|--|--|

| Number of Characters | 20 characters x 2 Lines | _                 |  |  |  |  |

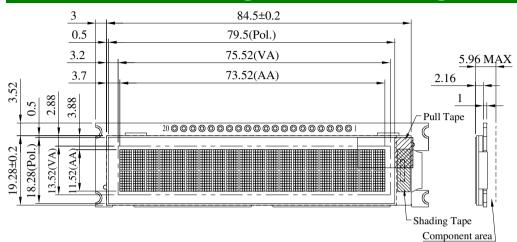

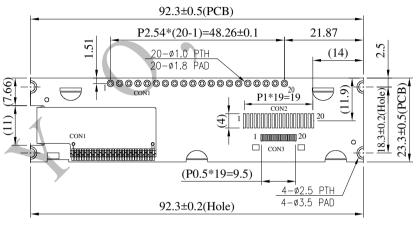

| Module dimension     | 92.3 x 23.3 x 5.96 Max. | mm                |  |  |  |  |

| Active area          | 73.52 x 11.52           | mm                |  |  |  |  |

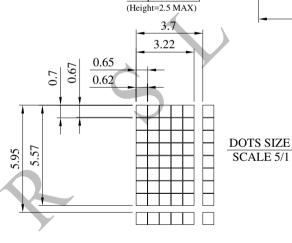

| Dot size             | 0.62 x 0.67             | mm                |  |  |  |  |

| Dot pitch            | 0.65 x 0.70             | mm                |  |  |  |  |

| Character size       | 3.22 x 5.57             | mm                |  |  |  |  |

| Character pitch      | 3.70 x 5.95             | mm                |  |  |  |  |

| Display type         | OLED , Monochrome       | OLED , Monochrome |  |  |  |  |

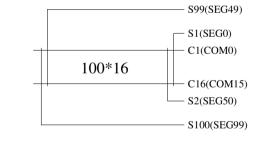

| Duty                 | 1/16                    |                   |  |  |  |  |

| IC                   | SSD1311                 |                   |  |  |  |  |

| Interface            | 6800,8080,SPI,I2C       |                   |  |  |  |  |

| Size                 | 2.93 inch               |                   |  |  |  |  |

#### **Contour Drawing & Block Diagram**

| PIN | SYMBOL | PIN | SYMBOL |

|-----|--------|-----|--------|

| 1   | VSS    | 11  | D4     |

| 2   | VDD    | 12  | D5     |

| 3   | REGVDD | 13  | D6     |

| 4   | D/C#   | 14  | D7     |

| 5   | R/W#   | 15  | CS#    |

| 6   | Е      | 16  | RES#   |

| 7   | D0     | 17  | BS0    |

| 8   | D1     | 18  | BS1    |

| 9   | D2     | 19  | BS2    |

| 10  | D3     | 20  | VSS    |

The non-specified tolerance of dimension is  $\pm 0.3$ mm.

SCALE 5/1

#### **Interface Pin Function**

| Pin No. | Symbol | Pin Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|---------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1       | VSS    | Р        | Ground pin. It must be connected to external ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 2       | VDD    | Р        | Power supply for core logic operation.<br>A capacitor should be connected between VDD and VSS under<br>all circumstances.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 3       | REGVDD | I        | Internal VDD regulator selection pin It must be connected to external ground.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 4       | D/C#   | I        | This pin is Data/Command control pin connecting to the MCU. When the pin is pulled HIGH, the data at D[7:0] will be interpreted as data.  When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register.  In I2C mode, this pin acts as SA0 for slave address selection. When serial interface is selected, this pin must be connected to VSS.                                                                                                                                               |  |  |  |  |

| 5       | R/W#   | ı        | This pin is read / write control input pin connecting to the MCU interface.  When 6800 interface mode is selected, this pin will be used as Read/Write (R/W#) selection input. Read mode will be carried out when this pin is pulled HIGH and write mode when LOW.  When 8080 interface mode is selected, this pin will be the Write (WR#) input. Data write operation is initiated when this pin is pulled LOW and the chip is selected.  When serial or I2C interface is selected, this pin must be connected to VSS. |  |  |  |  |

| 6       | E      |          | This pin is MCU interface input. When 6800 interface mode is selected, this pin will be used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled HIGH and the chip is selected. When 8080 interface mode is selected, this pin receives the Read (RD#) signal. Read operation is initiated when this pin is pulled LOW and the chip is selected. When serial or I2C interface is selected, this pin must be connected to VSS.                                                           |  |  |  |  |

| 7  | D0   |     | These pins are bi-directional data bus connecting to the MCU                                                                                                                                 |

|----|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8  | D1   |     | data bus.                                                                                                                                                                                    |

| 9  | D2   |     | Unused pins are recommended to tie LOW.                                                                                                                                                      |

| 10 | D3   |     | When serial interface mode is selected, D0 will be the serial clock                                                                                                                          |

| 11 | D4   | I/O | input: SCLK; D1 will be the serial data input: SID and D2 will be                                                                                                                            |

| 12 | D5   |     | the serial data output: SOD.                                                                                                                                                                 |

| 13 | D6   |     | When I2C mode is selected, D2, D1 should be tied together and                                                                                                                                |

| 14 | D7   |     | serve as SDAout, SDAin in application and D0 is the serial clock input, SCL.                                                                                                                 |

| 15 | CS#  | l   | This pin is the chip select input connecting to the MCU. The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW). In I2C mode, this pin must be connected to VSS. |

| 16 | RES# | I   | This pin is reset signal input. When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.                                         |

| 17 | BS0  |     | MCU bus interface selection pins. Select appropriate logic setting                                                                                                                           |

| 18 | BS1  |     | as described in the following table. BS2, BS1 and BS0 are pin select.                                                                                                                        |

|    |      |     | Bus Interface selection                                                                                                                                                                      |

| 19 | BS2  | I   | BS[2:0]   Interface                                                                                                                                                                          |

| 20 | VSS  | Р   | Ground pin. It must be connected to external ground.                                                                                                                                         |

### **Absolute Maximum Ratings**

| Item                     | Symbol  | Min  | Max | Unit |

|--------------------------|---------|------|-----|------|

| Supply Voltage For Logic | VDD-VSS | -0.3 | 3.6 | V    |

| Operating Temperature    | TOP     | -40  | +80 | °C   |

| Storage Temperature      | TST     | -40  | +85 | °C   |

### **Electrical Characteristics**

#### **DC Electrical Characteristics**

| Item                                 | Symbol  | Condition    | Min     | Тур | Max     | Unit |

|--------------------------------------|---------|--------------|---------|-----|---------|------|

| Supply Voltage For Logic             | VDD-VSS | <b>O</b> -   | 3.1     | 3.3 | 3.5     | V    |

| Input High Volt.                     | VIH     | <del>/</del> | 0.8xVDD | _   | _       | V    |

| Input Low Volt.                      | VIL     | _            | _       | _   | 0.2xVDD | V    |

| Output High Volt.                    | VOH     | IOH=-0.5mA   | 0.9xVDD | _   | _       | V    |

| Output Low Volt.                     | VOL     | IOL=0.5mA    | _       | _   | 0.1xVDD | V    |

| 50% Check Board operating<br>Current | IDD     | VDD=3.3V     | _       | 50  | 75      | mA   |