## WINSTAR Display

# **OLED SPECIFICATION**

Model No:

WEO006448B

## **General Specification**

| Item             | Dimension                 | Unit |  |  |  |

|------------------|---------------------------|------|--|--|--|

| Dot Matrix       | 64 x 48 Dots              | - ^  |  |  |  |

| Module dimension | 18.46 × 18.10 × 1.26      | mm   |  |  |  |

| Active Area      | 13.42 × 10.06             | mm   |  |  |  |

| Pixel Size       | 0.185 × 0.185             | mm   |  |  |  |

| Pixel Pitch      | 0.210 × 0.210             | mm   |  |  |  |

| Display Mode     | Passive Matrix            |      |  |  |  |

| Display Color    | Monochrome                |      |  |  |  |

| Drive Duty       | 1/48 Duty                 |      |  |  |  |

| IC               | SSD1315                   |      |  |  |  |

| Interface        | 6800, 8080, 4-Wire SPI, I | 2C   |  |  |  |

| Size             | 0.66 inch                 |      |  |  |  |

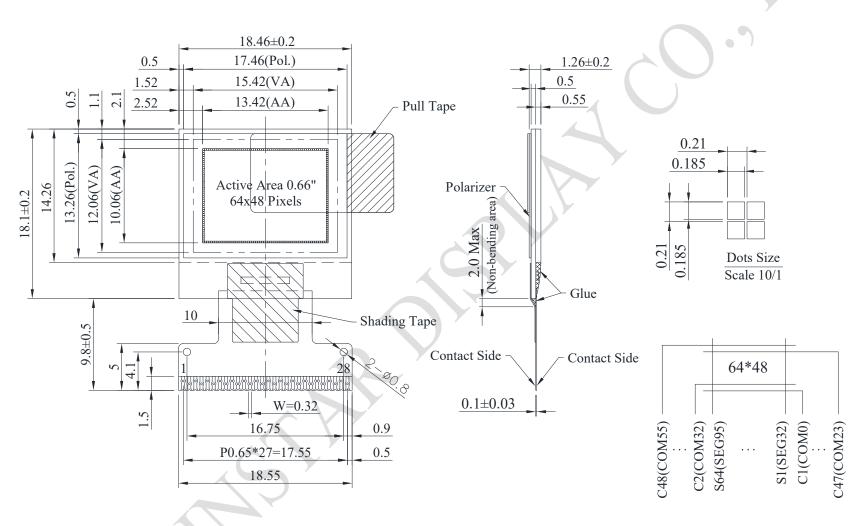

#### **Contour Drawing & Block Diagram**

| PIN | SYMBOL  |

|-----|---------|

| 1   | ESD_GND |

| 2   | C2N     |

| 3   | C2P     |

| 4   | C1P     |

| 5   | C1N     |

| 6   | VBAT    |

| 7   | VSS     |

| 8   | VDD     |

| 9   | BS1     |

| 10  | BS2     |

| 11  | CS#     |

| 12  | RES#    |

| 13  | D/C#    |

| 14  | R/W#    |

| 15  | E/RD#   |

| 16  | D0      |

| 17  | D1      |

| 18  | D2      |

| 19  | D3      |

| 20  | D4      |

| 21  | D5      |

| 22  | D6      |

| 23  | D7      |

| 24  | IREF    |

| 25  | VCOMH   |

| 26  | VCC     |

| 27  | VLSS    |

| 28  | ESD_GND |

The non-specified tolerance of dimension is  $\pm 0.3\ mm$  .

### **Interface Pin Function**

| No. | Symbol      | Function                                                                            |                                                                                    |             |                     |                        |                                                          |  |  |

|-----|-------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------|---------------------|------------------------|----------------------------------------------------------|--|--|

| 1   | ESD-GND     | It should be connected to ground.                                                   |                                                                                    |             |                     |                        |                                                          |  |  |

| 2   | C2N         | C1P/C1N – Pin for charge pump capacitor; Connect to each other with a               |                                                                                    |             |                     |                        |                                                          |  |  |

| 3   | C2P         | capacitor.                                                                          |                                                                                    |             |                     |                        |                                                          |  |  |

| 4   | C1P         | C2P/C2N – Pin for charge pump capacitor; Connect to each other with a               |                                                                                    |             |                     |                        |                                                          |  |  |

| 5   | C1N         | capacitor.                                                                          |                                                                                    |             |                     |                        |                                                          |  |  |

|     |             | Power supp                                                                          | Power supply for charge pump regulator circuit.                                    |             |                     |                        |                                                          |  |  |

|     |             | Status                                                                              | VBAT                                                                               |             | VDD                 |                        | vcc                                                      |  |  |

| 6   | VBAT        | Enable charge pump                                                                  | Connect to external VBAT source                                                    |             |                     | ect to external source | A capacitor should be connected between this pin and VSS |  |  |

|     |             | Disable                                                                             | Keep floa                                                                          | at          | Connect to external |                        | Connect to external VCC source                           |  |  |

|     |             | charge pump                                                                         | recop noc                                                                          |             |                     | source                 | Some to external voc source                              |  |  |

| 7   | VSS         | This is a gro                                                                       | und pi                                                                             | <br>า.      |                     | / \                    |                                                          |  |  |

| 8   | VDD         | Power supp                                                                          |                                                                                    |             | oaic o              | peration.              |                                                          |  |  |

| 9   | BS1         |                                                                                     |                                                                                    |             |                     | election input         |                                                          |  |  |

|     |             | See the follo                                                                       |                                                                                    |             |                     |                        |                                                          |  |  |

|     |             |                                                                                     |                                                                                    | BS1         | BS2                 | ]                      |                                                          |  |  |

|     |             | I2C                                                                                 |                                                                                    | 1           | 0                   |                        |                                                          |  |  |

| 10  | BS2         | 4-wire SPI                                                                          |                                                                                    | 0           | 0                   |                        |                                                          |  |  |

|     |             | 8-bit 6800 Pa                                                                       | rallel                                                                             | 0           | 1                   |                        |                                                          |  |  |

|     |             | 8-bit 8080 Pa                                                                       |                                                                                    | 1           | 1                   |                        |                                                          |  |  |

| 11  | CS#         | The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW). |                                                                                    |             |                     |                        |                                                          |  |  |

| 12  | DEC#        | This pin is re                                                                      | This pin is reset signal input. When the pin is low, initialization of the chip is |             |                     |                        |                                                          |  |  |

| 12  | KES#        | RES# executed. Keep this pin HIGH (i.e. connect to VDD) during normal operation.    |                                                                                    |             |                     |                        |                                                          |  |  |

|     |             | This pin is Data/Command control pin connecting to the MCU.                         |                                                                                    |             |                     |                        |                                                          |  |  |

| 13  | D/C#        | When the pin is pulled HIGH, the data at D[7:0] will be interpreted as data.        |                                                                                    |             |                     |                        |                                                          |  |  |

|     |             | When the pin is pulled LOW, the data at D[7:0] will be transferred                  |                                                                                    |             |                     |                        |                                                          |  |  |

|     |             | This is read / write control input pin connecting to the MCU interface.             |                                                                                    |             |                     |                        |                                                          |  |  |

|     |             | When interfacing to a 6800-series microprocessor, this pin will be used as          |                                                                                    |             |                     |                        |                                                          |  |  |

|     |             | Read/Write (R/W#) selection input. Read mode will be carried out when this          |                                                                                    |             |                     |                        |                                                          |  |  |

| 14  | R/W#        | pin is pulled HIGH (i.e. connect to VDD) and write mode when LOW.                   |                                                                                    |             |                     |                        |                                                          |  |  |

|     |             |                                                                                     | When 8080 interface mode is selected, this pin will be the Write (WR#) input.      |             |                     |                        |                                                          |  |  |

|     |             |                                                                                     | peratio                                                                            | n is initia | atea v              | men this pin           | is pulled LOW and the chip is                            |  |  |

|     | <b>&gt;</b> | selected.                                                                           |                                                                                    |             |                     |                        |                                                          |  |  |

|     |             | When serial or I2C interface is selected, this pin must be connected to VSS.        |                                                                                    |             |                     |                        |                                                          |  |  |

| 15    | E/RD#   | This pin is MCU interface input. When 6800 interface mode is selected, this pin will be used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled HIGH and the chip is selected. When 8080 interface mode is selected, this pin receives the Read (RD#) signal. Read operation is initiated when this pin is pulled LOW and the chip is selected. When serial or I2C interface is selected, this pin must be connected to VSS. |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16~23 | D0~D7   | These are 8-bit bi-directional data bus to be connected to the microprocessor's data bus. When serial interface mode is selected, D0 will be the serial clock input: SCLK; D1 will be the serial data input: SDIN. When I2C mode is selected, D2, D1 should be tied together and serve as SDAout, SDAin in application and D0 is the serial clock input, SCL.                                                                                                 |

| 24    | IREF    | This is segment output current reference pin. When external IREF is used, a resistor should be connected between this pin and VSS to maintain the IREF current at 30uA. When internal IREF is used, this pin should be kept NC.                                                                                                                                                                                                                               |

| 25    | VCOMH   | COM signal deselected voltage level. A capacitor should be connected between this pin and VSS.                                                                                                                                                                                                                                                                                                                                                                |

| 26    | VCC     | Power supply for panel driving voltage. This is also the most positive power voltage supply pin. When charge pump is enabled, a capacitor should be connected between this pin and VSS.                                                                                                                                                                                                                                                                       |

| 27    | VLSS    | This is an analog ground pin. It should be connected to VSS externally.                                                                                                                                                                                                                                                                                                                                                                                       |

| 28    | ESD GND | It should be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **Absolute Maximum Ratings**

| Parameter                            | Symbol | Min | Max  | Unit |

|--------------------------------------|--------|-----|------|------|

| Supply Voltage                       | VDD    | 0   | 4.0  | V    |

| Charge Pump Regulator Supply Voltage | VBAT   | 0   | 6.0  | V    |

| Supply Voltage for Display           | VCC    | 0   | 18.0 | V    |

| Operating Temperature                | TOP    | -30 | +70  | °C   |

| Storage Temperature                  | TSTG   | -30 | +70  | °C   |

### **Electrical Characteristics**

| Item                                                                 | Symbol             | Condition   | Min     | Тур | Max     | Unit |

|----------------------------------------------------------------------|--------------------|-------------|---------|-----|---------|------|

| Supply Voltage for Logic                                             | VDD                |             | 1.65    | 3.0 | 3.3     | V    |

| Supply Voltage for Display (Supplied Externally)                     | VCC                | \           | 6.0     | 7.5 | 8.0     | V    |

| Charge Pump Regulator<br>Supply Voltage                              | VBAT               | <b>5</b> ′- | 3.0     | 3.3 | 4.5     | V    |

| Charge Pump Output Voltage for Display (Generated by Internal DC/DC) | Charge Pump<br>VCC |             | 7.0     | 7.5 | _       | V    |

| Input High Volt.                                                     | VIH                | _           | 0.8×VDD | _   | VDD     | V    |

| Input Low Volt.                                                      | VIL                | _           | 0       | _   | 0.2×VDD | V    |

| Output High Volt.                                                    | VOH                | _           | 0.9×VDD | _   | VDD     | V    |

| Output Low Volt.                                                     | VOL                | _           | 0       | _   | 0.1×VDD | V    |

| Display 50% Pixel on (VCC Supplied Externally)                       | ICC                | VCC=7.5V    | _       | 3   | 6       | mA   |

| Display 50% Pixel on<br>(VCC Generated by<br>Internal DC/DC)         | IBAT               | _           | _       | 15  | 30      | mA   |