|                                        |                         |

|----------------------------------------|-------------------------|

| <b>V<sub>DSS</sub></b>                 | <b>100V</b>             |

| <b>R<sub>DS(on)</sub> typ.</b>         | <b>4.8mΩ</b>            |

| <b>max.</b>                            | <b>6.0mΩ</b>            |

| <b>I<sub>D</sub> (Silicon Limited)</b> | <b>134A<sup>①</sup></b> |

| <b>I<sub>D</sub> (Package Limited)</b> | <b>120A</b>             |

## Applications

- High Efficiency Synchronous Rectification in SMPS

- Uninterruptible Power Supply

- High Speed Power Switching

- Hard Switched and High Frequency Circuits

## Benefits

- Improved Gate, Avalanche and Dynamic dv/dt Ruggedness

- Fully Characterized Capacitance and Avalanche SOA

- Enhanced body diode dV/dt and dI/dt Capability

- Lead-Free

| Base Part Number | Package Type | Standard Pack |          | Orderable Part Number |

|------------------|--------------|---------------|----------|-----------------------|

|                  |              | Form          | Quantity |                       |

| IRFP4310ZPbF     | TO-247       | Tube          | 25       | IRFP4310ZPbF          |

## Absolute Maximum Ratings

| Symbol                                  | Parameter                                                           | Max.              | Units |

|-----------------------------------------|---------------------------------------------------------------------|-------------------|-------|

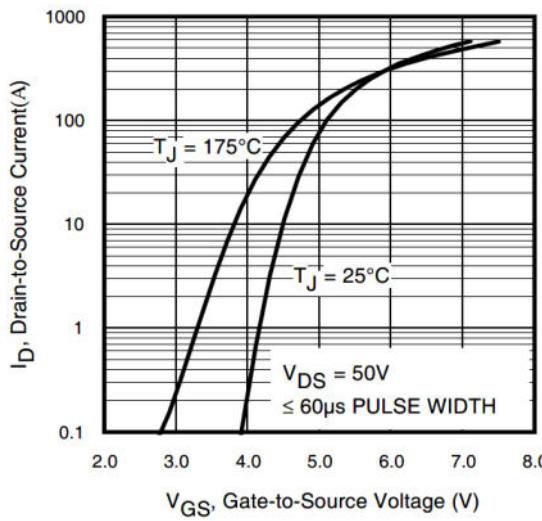

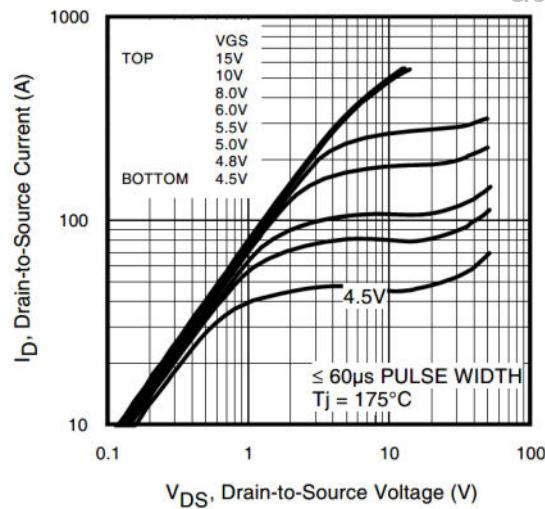

| I <sub>D</sub> @ T <sub>C</sub> = 25°C  | Continuous Drain Current, V <sub>GS</sub> @ 10V (Silicon Limited)   | 134 <sup>①</sup>  | A     |

| I <sub>D</sub> @ T <sub>C</sub> = 100°C | Continuous Drain Current, V <sub>GS</sub> @ 10V (Silicon Limited)   | 95                |       |

| I <sub>D</sub> @ T <sub>C</sub> = 25°C  | Continuous Drain Current, V <sub>GS</sub> @ 10V (Wire Bond Limited) | 120               |       |

| I <sub>DM</sub>                         | Pulsed Drain Current <sup>②</sup>                                   | 560               |       |

| P <sub>D</sub> @ T <sub>C</sub> = 25°C  | Maximum Power Dissipation                                           | 280               | W     |

|                                         | Linear Derating Factor                                              | 1.9               | W/°C  |

| V <sub>GS</sub>                         | Gate-to-Source Voltage                                              | ± 20              | V     |

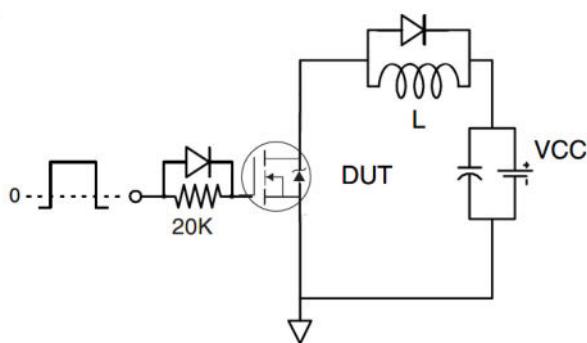

| dv/dt                                   | Peak Diode Recovery <sup>④</sup>                                    | 18                | V/ns  |

| T <sub>J</sub>                          | Operating Junction and                                              | -55 to + 175      | °C    |

| T <sub>STG</sub>                        | Storage Temperature Range                                           |                   |       |

|                                         | Soldering Temperature, for 10 seconds<br>(1.6mm from case)          |                   |       |

|                                         | Mounting torque, 6-32 or M3 screw                                   | 300               |       |

|                                         |                                                                     | 10lbf.in (1.1N·m) |       |

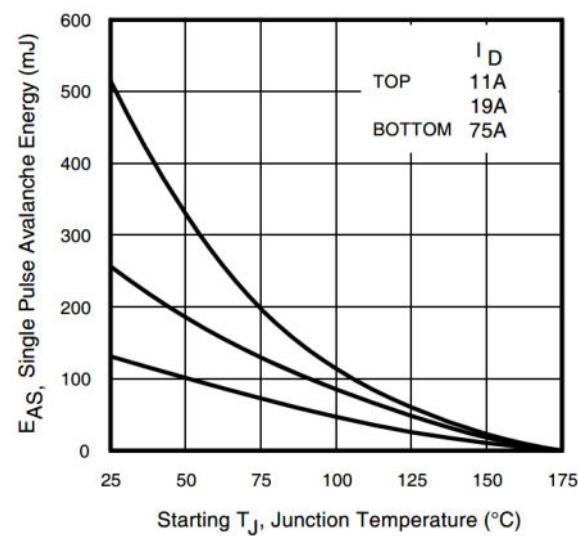

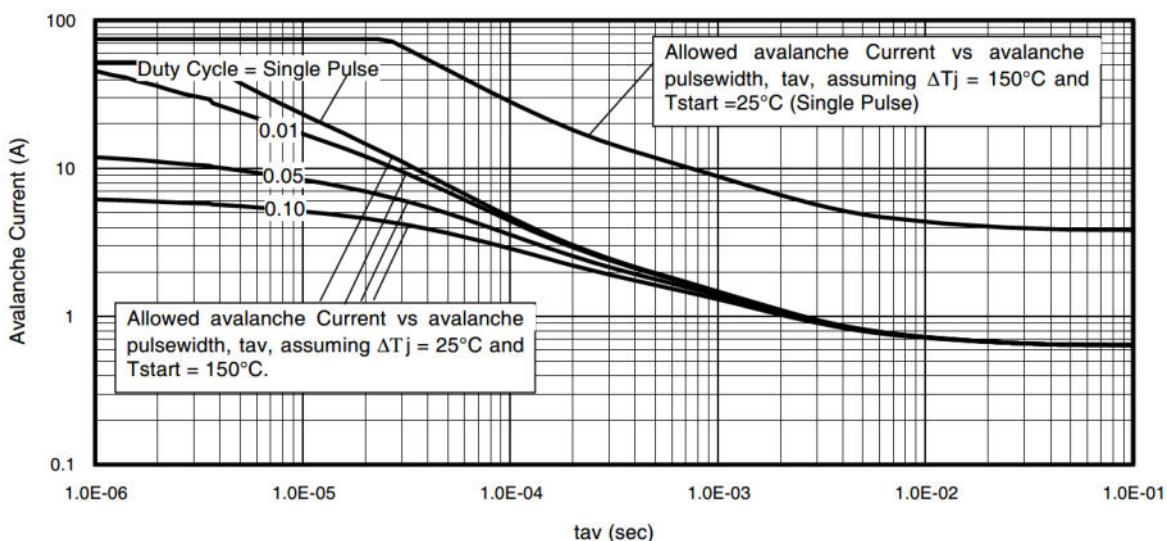

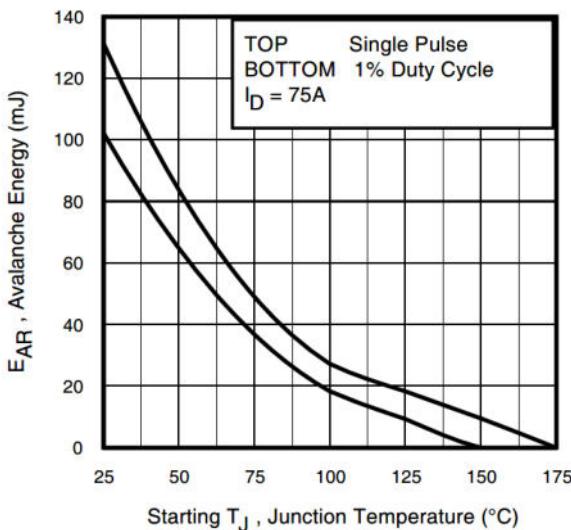

## Avalanche Characteristics

|                                     |                                            |                           |    |

|-------------------------------------|--------------------------------------------|---------------------------|----|

| E <sub>AS</sub> (Thermally limited) | Single Pulse Avalanche Energy <sup>③</sup> | 130                       | mJ |

| I <sub>AR</sub>                     | Avalanche Current <sup>②</sup>             | See Fig. 14, 15, 22a, 22b | A  |

| E <sub>AR</sub>                     | Repetitive Avalanche Energy <sup>⑤</sup>   |                           | mJ |

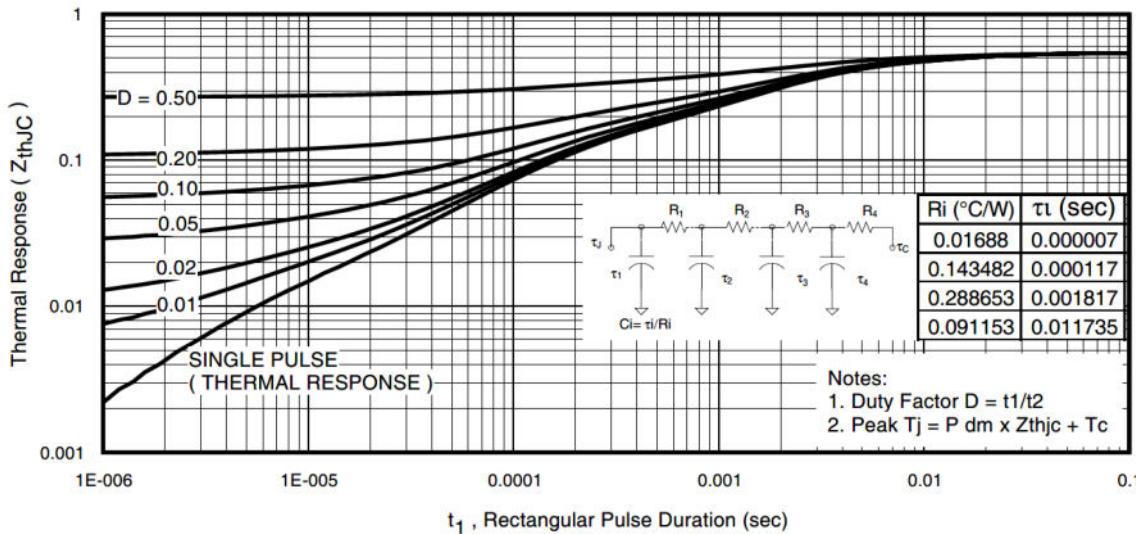

## Thermal Resistance

| Symbol           | Parameter                          | Typ. | Max. | Units |

|------------------|------------------------------------|------|------|-------|

| R <sub>θJC</sub> | Junction-to-Case <sup>⑥</sup>      | —    | 0.54 | °C/W  |

| R <sub>θCS</sub> | Case-to-Sink, Flat Greased Surface | 0.24 | —    |       |

| R <sub>θJA</sub> | Junction-to-Ambient <sup>⑥</sup>   | —    | 40   |       |

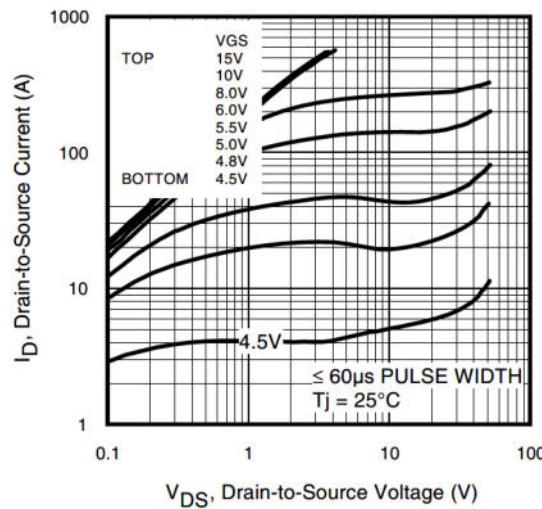

Static @  $T_J = 25^\circ\text{C}$  (unless otherwise specified)

| Symbol                                        | Parameter                            | Min. | Typ. | Max. | Units               | Conditions                                                                             |

|-----------------------------------------------|--------------------------------------|------|------|------|---------------------|----------------------------------------------------------------------------------------|

| $V_{(\text{BR})\text{DSS}}$                   | Drain-to-Source Breakdown Voltage    | 100  | —    | —    | V                   | $V_{\text{GS}} = 0\text{V}$ , $I_D = 250\mu\text{A}$                                   |

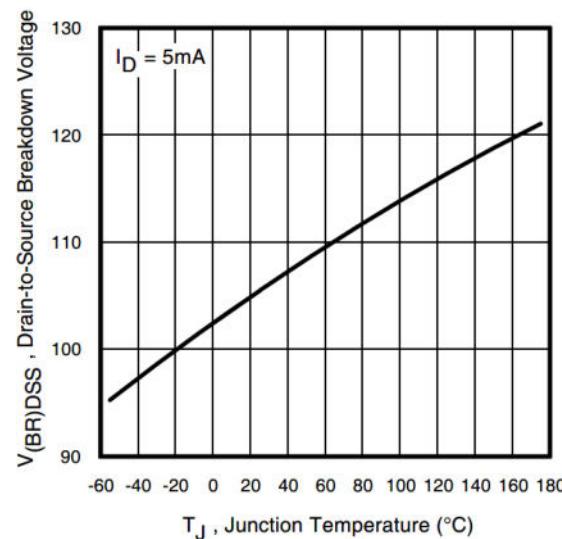

| $\Delta V_{(\text{BR})\text{DSS}}/\Delta T_J$ | Breakdown Voltage Temp. Coefficient  | —    | 0.11 | —    | V/ $^\circ\text{C}$ | Reference to $25^\circ\text{C}$ , $I_D = 5\text{mA}$ ②                                 |

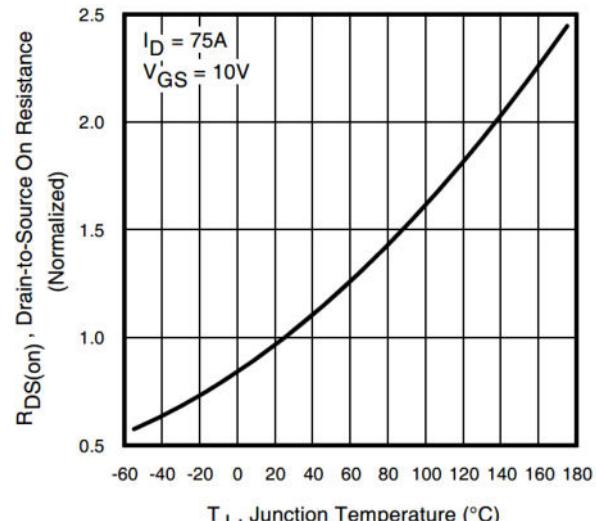

| $R_{\text{DS}(\text{on})}$                    | Static Drain-to-Source On-Resistance | —    | 4.8  | 6.0  | $\text{m}\Omega$    | $V_{\text{GS}} = 10\text{V}$ , $I_D = 75\text{A}$ ⑤                                    |

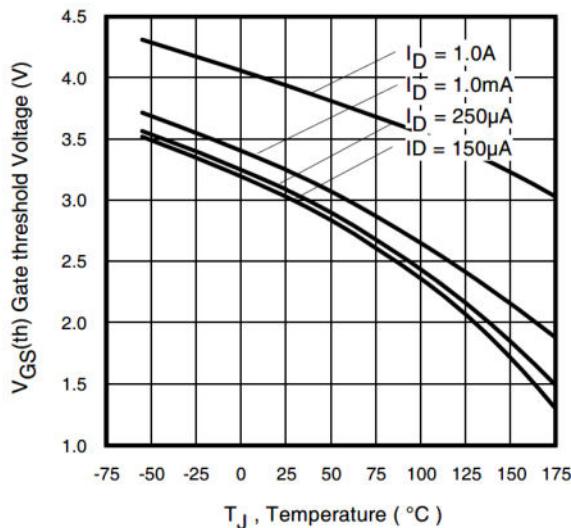

| $V_{\text{GS}(\text{th})}$                    | Gate Threshold Voltage               | 2.0  | —    | 4.0  | V                   | $V_{\text{DS}} = V_{\text{GS}}$ , $I_D = 150\mu\text{A}$                               |

| $I_{\text{DSS}}$                              | Drain-to-Source Leakage Current      | —    | —    | 20   | $\mu\text{A}$       | $V_{\text{DS}} = 100\text{V}$ , $V_{\text{GS}} = 0\text{V}$                            |

|                                               |                                      |      |      | 250  |                     | $V_{\text{DS}} = 80\text{V}$ , $V_{\text{GS}} = 0\text{V}$ , $T_J = 125^\circ\text{C}$ |

| $I_{\text{GSS}}$                              | Gate-to-Source Forward Leakage       | —    | —    | 100  | nA                  | $V_{\text{GS}} = 20\text{V}$                                                           |

|                                               | Gate-to-Source Reverse Leakage       | —    | —    | -100 |                     | $V_{\text{GS}} = -20\text{V}$                                                          |

| $R_G$                                         | Gate Resistance                      | —    | 0.7  | —    | $\Omega$            |                                                                                        |

Dynamic @  $T_J = 25^\circ\text{C}$  (unless otherwise specified)

| Symbol                     | Parameter                                           | Min. | Typ. | Max. | Units | Conditions                                                                                |

|----------------------------|-----------------------------------------------------|------|------|------|-------|-------------------------------------------------------------------------------------------|

| $g_{\text{fs}}$            | Forward Transconductance                            | 150  | —    | —    | S     | $V_{\text{DS}} = 50\text{V}$ , $I_D = 75\text{A}$                                         |

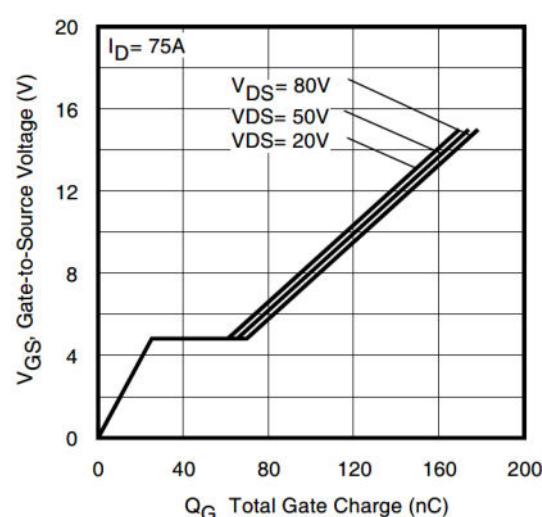

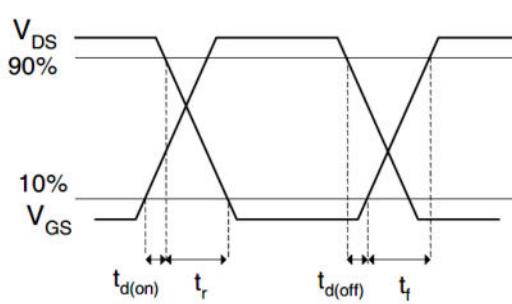

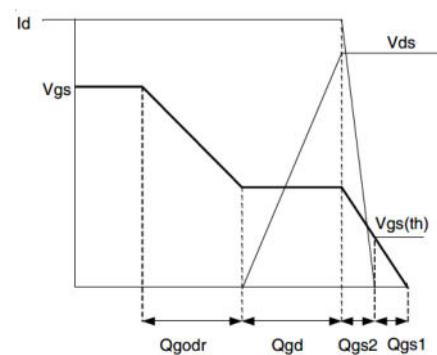

| $Q_g$                      | Total Gate Charge                                   | —    | 120  | 170  | nC    | $I_D = 75\text{A}$                                                                        |

| $Q_{\text{gs}}$            | Gate-to-Source Charge                               | —    | 29   | —    |       | $V_{\text{DS}} = 50\text{V}$                                                              |

| $Q_{\text{gd}}$            | Gate-to-Drain ("Miller") Charge                     | —    | 35   | —    |       | $V_{\text{GS}} = 10\text{V}$ ⑤                                                            |

| $Q_{\text{gsync}}$         | Total Gate Charge Sync. ( $Q_g$ - $Q_{\text{gd}}$ ) | —    | 85   | —    |       | $I_D = 75\text{A}$ , $V_{\text{DS}} = 50\text{V}$ , $V_{\text{GS}} = 10\text{V}$          |

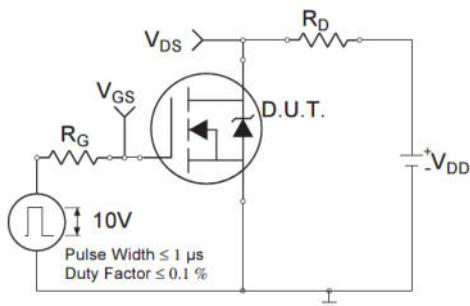

| $t_{\text{d}(\text{on})}$  | Turn-On Delay Time                                  | —    | 20   | —    | ns    | $V_{\text{DD}} = 65\text{V}$                                                              |

| $t_r$                      | Rise Time                                           | —    | 60   | —    |       | $I_D = 75\text{A}$                                                                        |

| $t_{\text{d}(\text{off})}$ | Turn-Off Delay Time                                 | —    | 55   | —    |       | $R_G = 2.7\Omega$                                                                         |

| $t_f$                      | Fall Time                                           | —    | 57   | —    |       | $V_{\text{GS}} = 10\text{V}$ ⑤                                                            |

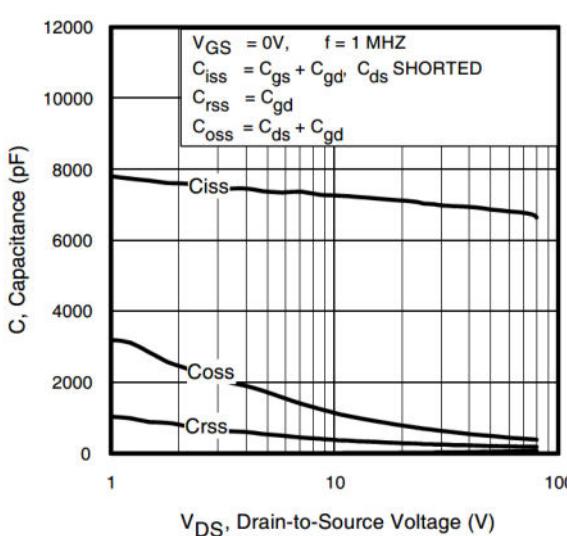

| $C_{\text{iss}}$           | Input Capacitance                                   | —    | 6860 | —    | pF    | $V_{\text{GS}} = 0\text{V}$                                                               |

| $C_{\text{oss}}$           | Output Capacitance                                  | —    | 490  | —    |       | $V_{\text{DS}} = 50\text{V}$                                                              |

| $C_{\text{rss}}$           | Reverse Transfer Capacitance                        | —    | 220  | —    |       | $f = 1.0\text{ MHz}$ , See Fig. 5                                                         |

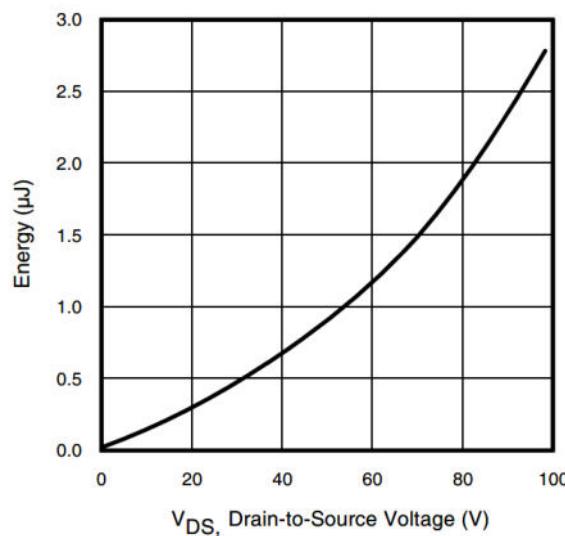

| $C_{\text{oss eff. (ER)}}$ | Effective Output Capacitance (Energy Related) ⑦     | —    | 570  | —    |       | $V_{\text{GS}} = 0\text{V}$ , $V_{\text{DS}} = 0\text{V}$ to $80\text{V}$ , See Fig. 11 ⑦ |

| $C_{\text{oss eff. (TR)}}$ | Effective Output Capacitance (Time Related) ⑥       | —    | 920  | —    |       | $V_{\text{GS}} = 0\text{V}$ , $V_{\text{DS}} = 0\text{V}$ to $80\text{V}$ ⑥               |

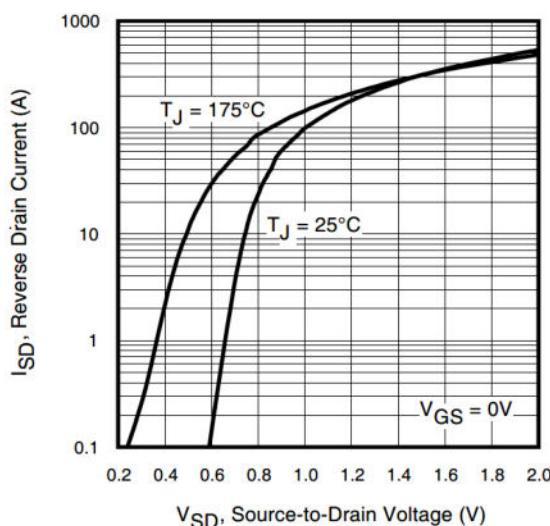

## Diode Characteristics

| Symbol           | Parameter                              | Min.                                                                        | Typ. | Max.  | Units | Conditions                                                                            |

|------------------|----------------------------------------|-----------------------------------------------------------------------------|------|-------|-------|---------------------------------------------------------------------------------------|

| $I_s$            | Continuous Source Current (Body Diode) | —                                                                           | —    | 134 ① | A     | MOSFET symbol showing the integral reverse p-n junction diode.                        |

| $I_{\text{SM}}$  | Pulsed Source Current (Body Diode) ②   | —                                                                           | —    | 560   |       |  |

| $V_{\text{SD}}$  | Diode Forward Voltage                  | —                                                                           | —    | 1.3   | V     | $T_J = 25^\circ\text{C}$ , $I_s = 75\text{A}$ , $V_{\text{GS}} = 0\text{V}$ ⑤         |

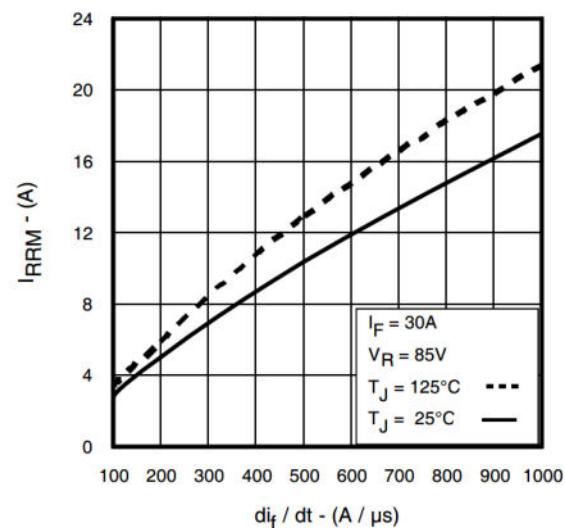

| $t_{\text{rr}}$  | Reverse Recovery Time                  | —                                                                           | 40   | —     | ns    | $T_J = 25^\circ\text{C}$                                                              |

|                  |                                        | —                                                                           | 49   | —     |       | $T_J = 125^\circ\text{C}$                                                             |

| $Q_{\text{rr}}$  | Reverse Recovery Charge                | —                                                                           | 58   | —     | nC    | $T_J = 25^\circ\text{C}$                                                              |

|                  |                                        | —                                                                           | 89   | —     |       | $T_J = 125^\circ\text{C}$                                                             |

| $I_{\text{RRM}}$ | Reverse Recovery Current               | —                                                                           | 2.5  | —     | A     | $T_J = 25^\circ\text{C}$                                                              |

| $t_{\text{on}}$  | Forward Turn-On Time                   | Intrinsic turn-on time is negligible (turn-on is dominated by $L_s + L_D$ ) |      |       |       |                                                                                       |

## Notes:

- ① Calculated continuous current based on maximum allowable junction temperature. Bond wire current limit is 120A. Note that current limitations arising from heating of the device leads may occur with some lead mounting arrangements. (Refer to AN-1140)

- ② Repetitive rating; pulse width limited by max. Junction temperature.

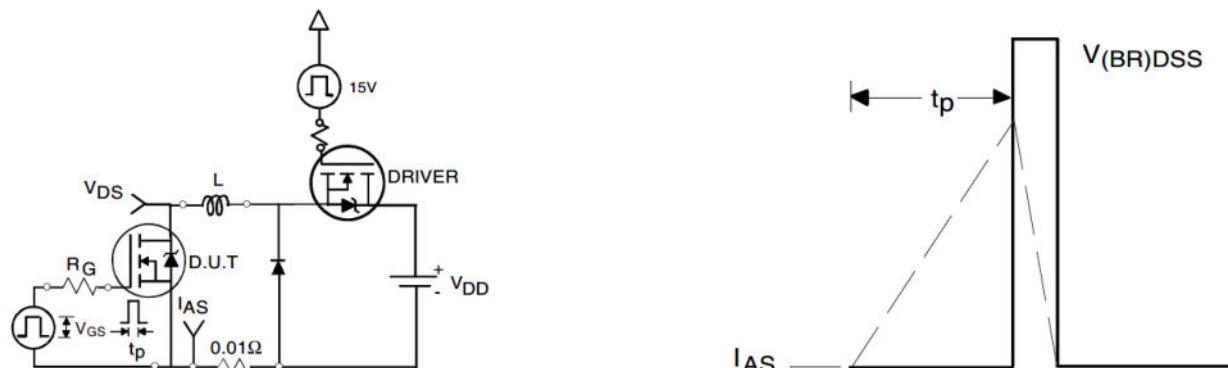

- ③ Limited by  $T_{\text{Jmax}}$ , starting  $T_J = 25^\circ\text{C}$ ,  $L = 0.047\text{mH}$ ,  $R_G = 25\Omega$ ,  $I_{\text{AS}} = 75\text{A}$ ,  $V_{\text{GS}} = 10\text{V}$ . Part not Recommended for use above this value.

- ④  $I_{\text{SD}} \leq 75\text{A}$ ,  $\text{di}/\text{dt} \leq 600\text{A}/\mu\text{s}$ ,  $V_{\text{DD}} \leq V_{(\text{BR})\text{DSS}}$ ,  $T_J \leq 175^\circ\text{C}$ .

- ⑤ Pulse width  $\leq 400\mu\text{s}$ ; duty cycle  $\leq 2\%$ .

- ⑥ Coss eff. (TR) is a fixed capacitance that gives the same charging time as Coss while  $V_{\text{DS}}$  is rising from 0 to 80%  $V_{\text{DSS}}$ .

- ⑦ Coss eff. (ER) is a fixed capacitance that gives the same energy as Coss while  $V_{\text{DS}}$  is rising from 0 to 80%  $V_{\text{DSS}}$ .

- ⑧  $R_\theta$  is measured at  $T_J$  approximately  $90^\circ\text{C}$ .

Fig 7. Typical Source-to-Drain Diode Forward Voltage

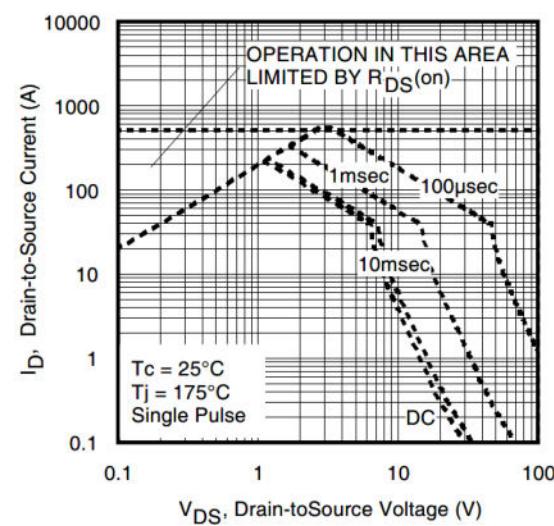

Fig 8. Maximum Safe Operating Area

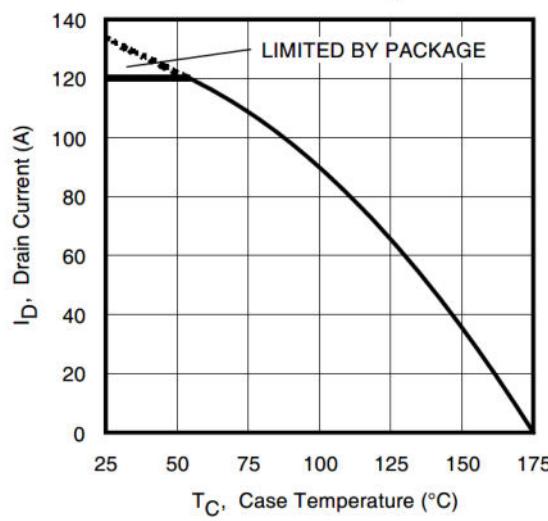

Fig 9. Maximum Drain Current vs. Case Temperature

Fig 10. Drain-to-Source Breakdown Voltage

Fig 11. Typical Coss Stored Energy

Fig 12. Maximum Avalanche Energy vs. Drain Current

Fig 13. Maximum Effective Transient Thermal Impedance, Junction-to-Case

Fig 14. Typical Avalanche Current vs. Pulsewidth

Notes on Repetitive Avalanche Curves , Figures 14, 15:

(For further info, see AN-1005 at [www.irf.com](http://www.irf.com))

1. Avalanche failures assumption:

Purely a thermal phenomenon and failure occurs at a temperature far in excess of  $T_{jmax}$ . This is validated for every part type.

2. Safe operation in Avalanche is allowed as long as  $T_{jmax}$  is not exceeded.

3. Equation below based on circuit and waveforms shown in Figures 16a, 16b.

4.  $P_{D(ave)}$  = Average power dissipation per single avalanche pulse.

5. BV = Rated breakdown voltage (1.3 factor accounts for voltage increase during avalanche).

6.  $I_{av}$  = Allowable avalanche current.

7.  $\Delta T$  = Allowable rise in junction temperature, not to exceed  $T_{jmax}$  (assumed as  $25^{\circ}\text{C}$  in Figure 14, 15).

- $t_{av}$  = Average time in avalanche.

- $D$  = Duty cycle in avalanche =  $t_{av} \cdot f$

- $Z_{thJC}(D, t_{av})$  = Transient thermal resistance, see Figures 13)

$$P_{D(ave)} = 1/2 ( 1.3 \cdot BV \cdot I_{av} ) = \Delta T / Z_{thJC}$$

$$I_{av} = 2\Delta T / [1.3 \cdot BV \cdot Z_{th}]$$

$$E_{AS(AR)} = P_{D(ave)} \cdot t_{av}$$

Fig 15. Maximum Avalanche Energy vs. Temperature

**Fig. 16** Threshold Voltage vs. Temperature

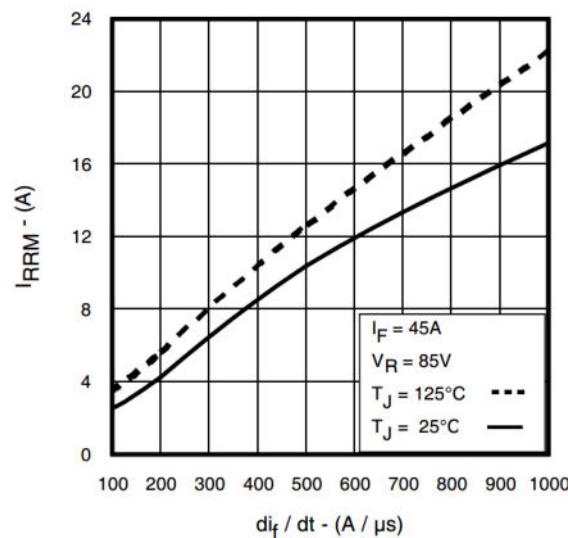

**Fig. 17** Typical Recovery Current vs.  $di_f/dt$

**Fig 18.** Typical Recovery Current vs.  $di_f/dt$

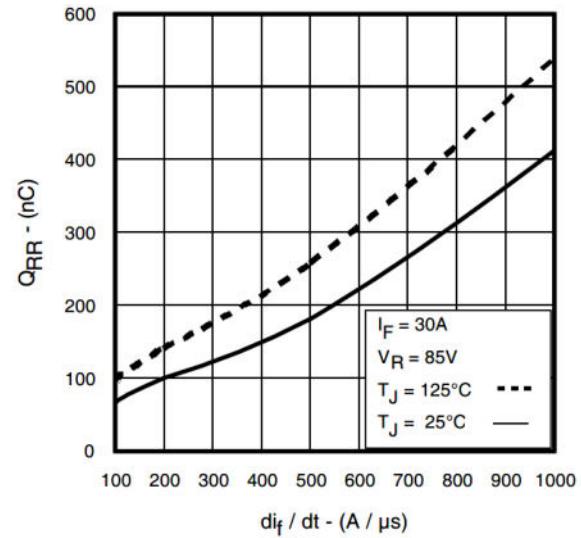

**Fig 19.** Typical Stored Charge vs.  $di_f/dt$

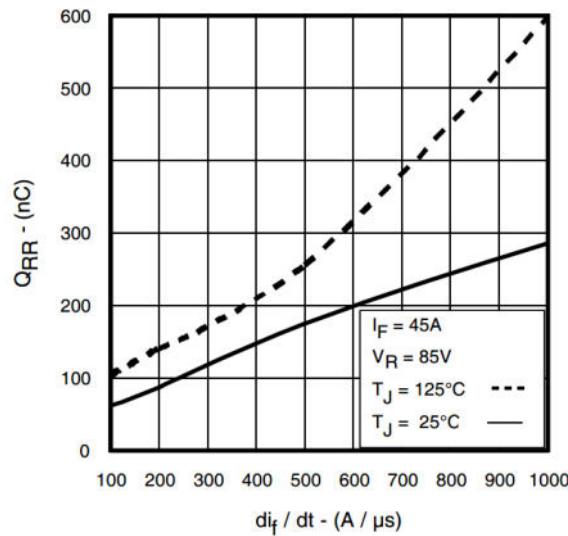

**Fig 20.** Typical Stored Charge vs.  $di_f/dt$

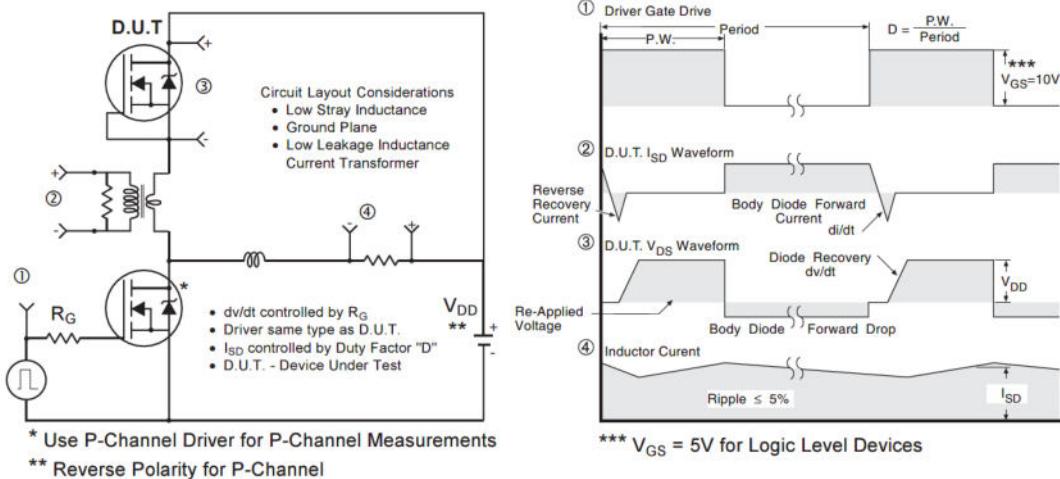

Fig 21. Peak Diode Recovery dv/dt Test Circuit for N-Channel HEXFET® Power MOSFETs

Fig 22a. Unclamped Inductive Test Circuit

Fig 22b. Unclamped Inductive Waveforms

Fig 23a. Switching Time Test Circuit

Fig 23b. Switching Time Waveforms

Fig 24a. Gate Charge Test Circuit

Fig 24b. Gate Charge Waveform

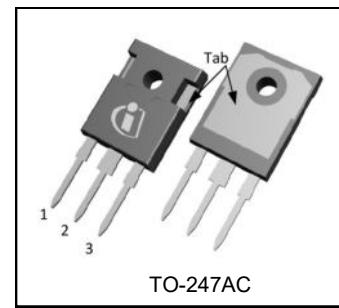

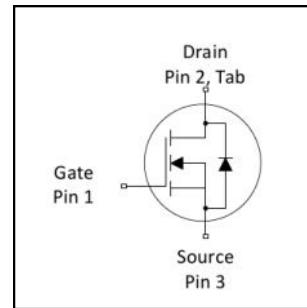

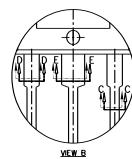

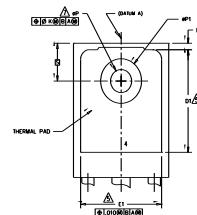

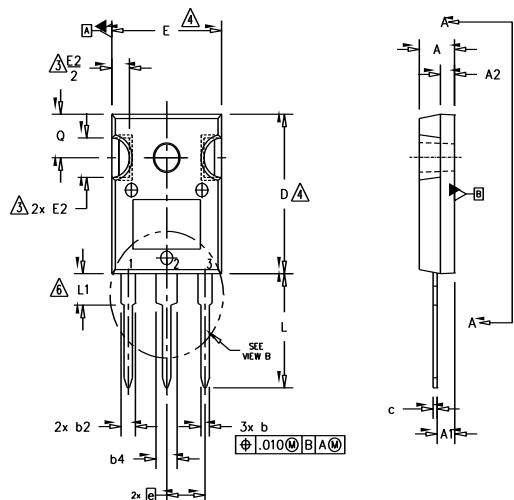

## TO-247AC Package Outline (Dimensions are shown in millimeters (inches))

VIEW B

SECTION O-O, D-D, E-E

NOTES:

1. DIMENSIONING AND TOLERANCING AS PER ASME Y14.5M 1994.

2. DIMENSIONS ARE SHOWN IN INCHES.

3. CONTOUR OF SLOT OPTIONAL.

4. DIMENSION D & E DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED .005" (0.127) PER SIDE. THESE DIMENSIONS ARE MEASURED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY.

5. THERMAL PAD CONTOUR OPTIONAL WITHIN DIMENSIONS D1 & E1.

6. LEAD FINISH UNCONTROLLED IN L1.

7. TO HAVE A MAXIMUM DRAFT ANGLE OF 1.5° TO THE TOP OF THE PART WITH A MAXIMUM HOLE DIAMETER OF .154 INCH.

8. OUTLINE CONFORMS TO JEDEC OUTLINE TO-247AC.

| SYMBOL | DIMENSIONS |      |             |       | NOTES |

|--------|------------|------|-------------|-------|-------|

|        | INCHES     |      | MILLIMETERS |       |       |

|        | MIN.       | MAX. | MIN.        | MAX.  |       |

| A      | .183       | .209 | 4.65        | 5.31  |       |

| A1     | .087       | .102 | 2.21        | 2.59  |       |

| A2     | .059       | .098 | 1.50        | 2.49  |       |

| b      | .039       | .055 | 0.99        | 1.40  |       |

| b1     | .039       | .053 | 0.99        | 1.35  |       |

| b2     | .065       | .094 | 1.65        | 2.39  |       |

| b3     | .065       | .092 | 1.65        | 2.34  |       |

| b4     | .102       | .135 | 2.59        | 3.43  |       |

| b5     | .102       | .133 | 2.59        | 3.38  |       |

| c      | .015       | .035 | 0.38        | 0.89  |       |

| c1     | .015       | .033 | 0.38        | 0.84  |       |

| D      | .776       | .815 | 19.71       | 20.70 | 4     |

| D1     | .515       | —    | 13.08       | —     | 5     |

| D2     | .020       | .053 | 0.51        | 1.35  |       |

| E      | .602       | .625 | 15.29       | 15.87 |       |

| E1     | .530       | —    | 13.46       | —     |       |

| E2     | .178       | .216 | 4.52        | 5.49  |       |

| e      | .215 BSC   |      | 5.46 BSC    |       |       |

| gk     | .010       |      | 0.25        |       |       |

| L      | .559       | .634 | 14.20       | 16.10 |       |

| L1     | .146       | .169 | 3.71        | 4.29  |       |

| gP     | .140       | .144 | 3.56        | 3.66  |       |

| gP1    | —          | .291 | —           | 7.39  |       |

| O      | .209       | .224 | 5.31        | 5.69  |       |

| S      | .217 BSC   |      | 5.51 BSC    |       |       |

LEAD ASSIGNMENTSHEXFET

1. GATE

2. DRAIN

3. SOURCE

4. DRAIN

IGBTs, CoPACK

1. GATE

2. COLLECTOR

3. Emitter

4. COLLECTOR

DIODES

1. ANODE/OPEN

2. CATHODE

3. ANODE

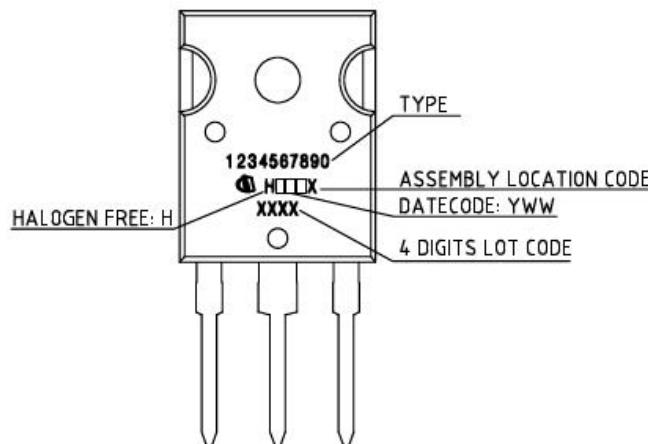

## TO-247AC Part Marking Information

TO-247AC package is not recommended for Surface Mount Application.

**Revision History**

| Date       | Rev. | Comments                                                                                                                                                              |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2013-09-06 | 2.0  | <ul style="list-style-type: none"><li>• Final data sheet</li></ul>                                                                                                    |

| 2024-12-05 | 2.1  | <ul style="list-style-type: none"><li>• Update datasheet to Infineon format</li><li>• Updated Part marking –page 8</li><li>• Added disclaimer on last page.</li></ul> |

## Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

## We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: [erratum@infineon.com](mailto:erratum@infineon.com)

## Published by

**Infineon Technologies AG**

**81726 München, Germany**

**© 2024 Infineon Technologies AG**

**All Rights Reserved.**

## Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics (“Beschaffenheitsgarantie”).

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

## Information

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office ([www.infineon.com](http://www.infineon.com)).

## Warnings

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

The Infineon Technologies component described in this Data Sheet may be used in life support devices or systems and or automotive, aviation and aerospace applications or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life support, automotive, aviation and aerospace device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.